Received 15 March 2024, accepted 6 May 2024, date of publication 13 May 2024, date of current version 23 May 2024.

Digital Object Identifier 10.1109/ACCESS.2024.3400685

# **Trustworthy Integrated Circuits: From Safety to Security and Beyond**

ENKELE RAMA<sup>10,1,\*</sup>, MOUADH AYACHE<sup>2,3,\*</sup>, RAINER BUCHTY<sup>10,3</sup>, BERNHARD BAUER<sup>4</sup>, MATTHIAS KORB<sup>1</sup>, (Senior Member, IEEE), MLADEN BEREKOVIC<sup>3</sup>, (Member, IEEE), AND SALEH MULHEM<sup>10,3</sup>

<sup>1</sup>Institute for Integrated Systems, University of the Bundeswehr Munich, 85577 Neubiberg, Germany

Corresponding authors: Mouadh Ayache (mouadh.ayache@synopsys.com) and Enkele Rama (enkele.rama@unibw.de)

This work was supported in part by German Ministry of Education and Research through the publicly funded VE-VIDES Project under Grant 16ME0251.

**ABSTRACT** The trustworthiness of integrated circuits (ICs) has become increasingly important due to the ubiquitousness of ICs and the insecure nature of the current semiconductor supply chain. Throughout development and operation, ICs are exposed to several risks that can arise from malicious actors or harsh operational conditions. Therefore, the question arises: Does the trustworthiness of an IC indicate its security only or other attributes beyond? Various disciplines may have a different understanding of what IC trustworthiness means. Thus, a compact and unified definition that provides its main overarching attributes is required. Such a definition would lead to a greater readiness to deal with emerging challenges. To define trustworthiness at IC level, we identify the minimum number of attributes required to cover the various perspectives of development, focusing on correct functionality, reliability, security, and functional safety. Subsequently, we review and provide a structured description of identified critical pre-silicion issues that can negatively impact the defined attributes. Besides academic literature, standards, and industry-relevant publications, we consider industry experts' opinions to achieve the maximum possible coverage of our topical review. We also provide an overview and analysis of several existing evaluation methodologies of the respective trustworthiness attributes, as evaluating the discussed issues is another important aspect for achieving trustworthiness. Our findings highlight the need for a comprehensive and universally applicable framework to evaluate the trustworthiness of ICs.

INDEX TERMS EDA, integrated circuit design, reliability, safety, security, trustworthiness.

### I. INTRODUCTION

Integrated Circuits (ICs) have become critical in enabling applications that affect every aspect of modern life. They are more complex and subject to stringent requirements for Power, Performance, and Area (PPA). Furthermore, new process nodes introduce additional reliability concerns. The use of ICs in security and safety-critical applications, such as data centers, automotive, healthcare, adds another layer of complexity. Meeting the requirements that arise from these challenges under tight development schedules has become

The associate editor coordinating the review of this manuscript and approving it for publication was Leandros Maglaras.

increasingly difficult for IC developers. To address these various challenges, a comprehensive approach is necessary that balances these aspects throughout the IC lifecycle. Efforts to reconcile all these aspects have led to the emergence of the concept of trustworthiness.

Trustworthiness has become the backbone of several research and development strategies. For example, multiple research projects targeting trustworthy electronics have been funded in Europe, including ZEUS by the German Federal Ministry of Education and Research (BMBF) [1]. In the US, the Defense Advanced Research Projects Agency (DARPA) is funding many research projects on the system trustworthiness. In 2017, DARPA announced a five-year

<sup>&</sup>lt;sup>2</sup>Synopsys GmbH, 85609 Aschheim, Germany

<sup>&</sup>lt;sup>3</sup>Institute of Computer Engineering, University of Lübeck, 23562 Lübeck, Germany

<sup>&</sup>lt;sup>4</sup>CARIAD SE, 80807 Munich, Germany

<sup>\*</sup>Enkele Rama and Mouadh Ayache are co-first authors.

plan to invest 1.5 billion US dollars in the advancement of the US semiconductor industry [2]. Furthermore, in 2022, DARPA took a step towards funding projects aimed at trustworthy artificial intelligence [3] and the trust of computing systems [4]. Therefore, a clear interpretation and formalization of trustworthiness in the context of electronics, and specifically ICs, is also required.

In their infancy, during the 1940s, digital computers were developed with largely unreliable components [5]. These components introduced faults that resulted in failures. One method of overcoming these failures was the use of redundant components. Various redundancy theories were unified under the concept of failure tolerance in 1965 [6]. Later, in 1982, a special session on fundamental concepts of fault tolerance was held at International Symposium on Fault-Tolerant Computing (FTCS)-12 [7], where various proposals were made to offer a consistent concept and terminology for fault tolerance. An encompassing concept for these proposals became necessary. Thus, between 1985 and 1992, Jean-Claude Laprie worked on developing the concept of dependability and led a great effort to define the basic concepts and terminology in this domain [8], [9]. In one of the first works in 1985, Laprie defined dependability to essentially encompass availability and reliability [10]. However, this definition cannot distinguish between availability and reliability in special cases, such as in the case of nonrepairable systems [11], where availability reduces to reliability, as repairs after failure are not possible. Subsequently, Laprie expanded his definition of dependability by adding safety and security [9]. In [9], intentional faults, e.g., the insertion of malicious logic, were first introduced. Since then, intentional faults, as security threats, have been considered in conjunction with reliability issues. This motivated a new paradigm of computing, called dependable computing, which has been extended over the years to various domains. The Institute of Electrical and Electronics Engineers (IEEE) P2851 Working Group, which created the IEEE Standard for Functional Safety Data Format for Interoperability within the Dependability Lifecycle [12], interprets the dependability of autonomous machines as "the property of an autonomous machine to perform reliably, safely, securely, in a timedeterministic manner, etc." [13]. Dependability, motivated by reliability, is an attempt to unify the various different terms, especially related to fault tolerance, into a common

**Trustworthiness**, meanwhile, has various definitions. In some works, such as in [5], trustworthiness is considered to be equivalent to dependability, where both concepts are considered to have the same goal: "[the] assurance that a system will perform as expected". In other works, such as in [14], the International Federation for Information Processing (IFIP) Working Group 10.4 on Dependable Computing and Fault Tolerance uses trustworthiness to define dependability as: "the trustworthiness of a computing system which allows reliance to be justifiably placed on the service it delivers".

Still, the aspect of security is consistently incorporated into the definition of trustworthiness. Both the US National Institute for Standards and Technology (NIST) [15] and the German Federal Ministry for Economic Affairs and Energy (BMWi) [16] consider security to be the underlying prerequisite for trustworthiness. In [5], similarities and differences between dependability and trustworthiness were investigated, where threats are development, physical, and instruction faults from the perspective of dependability, while threats are hostile attacks, environmental disruptions, and human errors from the perspective of trustworthiness [17]. Although the definition of trustworthiness differs depending on the application and the defining entity, both terms are often interchangeably used, and there is no universally agreed-upon definition across domains [18].

#### LIST OF ABBREVIATIONS

| ΑI  | Artificial Intelligence |

|-----|-------------------------|

| AoU | Assumptions of Use      |

**ASIL** Automotive Safety Integrity Level

**BIST** Build-in Self Test

**CIA** Confidentiality, Integrity and Availability

**CWE** Common Weakness Enumeration

DAL Design Assurance LevelDCLS Dual-Core Lockstep

DFA Dependent Failure AnalysisDFT Design for TestabilityDoS Denial of Service

DRC Design Rule Check

EDA Electronic Design Automation

ECU Electronic Control Unit

FFI Freedom from Interference

**FMEA** Failure Modes and Effects Analysis

**FMECA** Failure Modes, Effects, and Criticality Analysis **FMEDA** Failure Modes, Effects, and Diagnostic Analysis

**FPGA** Field Programmable Gate Array

**FTA** Fault Tree Analysis

**HARA** Hazard Analysis and Risk Assessment

IC Integrated Circuit

I/O Input/Output

IoT Internet of Things

IP Intellectual Property

LVS Layout Versus Schematic

**OEM** Original Equipment Manufacturer

PDK Process Design Kit

**PPA** Power, Performance, and Area

RTL Register-Transfer Level

**SEooC** Safety Element out of Context

SIL Safety Integrity Level

SM Safety Mechanism

SoC System-on-Chip

There are attempts to provide a comprehensive definition of trustworthiness at the *system level*. Where by system we mean "an entity that interacts with other entities, i.e., other systems, including hardware, software, humans, and the

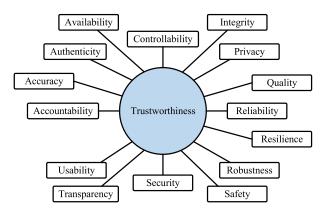

FIGURE 1. Characteristics of trustworthiness of a system per ISO/IEC TS 5723:2022.

physical world with its natural phenomena [5], to achieve one or more stated purposes" [19]. In electronics, such a system could be an Electronic Control Unit (ECU) used in a car. At the system level, the recent standard International Organization for Standardization (ISO)/International Electrotechnical Commission (IEC) TS 5723:2022 [19] provides a definition of trustworthiness for systems, where trustworthiness is defined as "the ability to meet stakeholders" expectations in a verifiable way". The various characteristics that trustworthiness can have, according to this definition, are shown in Fig. 1. Table 1, part (a), summarizes the definitions of the characteristics extracted from the ISO/IECTS 5723:2022 [19]. In addition to the characteristics defined in the aforementioned standard, the characteristics of confidentiality, maintainability, serviceability, and repairability are included in part (b) of Table 1, since they are important in the context of electronic systems and, by extension, for ICs.

In this paper, we are specifically interested in what trustworthiness means in the context of ICs. As an IC represents a subsystem or component, we analyze trustworthiness at the *subsystem level* and investigate what can undermine it. In this case, the definition of trustworthiness relies on: (1) preventing security-related threats, such as hostile attacks [17], fault injection attacks, hardware Trojans, and Intellectual Property (IP) theft, including piracy and counterfeiting [24]; and (2) mitigating the effects of failure modes, such as complete and partial failures, or catastrophic and degraded failures [11]. Therefore, designing trustworthy ICs requires a deep understanding of security threats on the one hand and what makes a system fault-free and functionally correct on the other. In the following, we look at how trustworthiness is viewed from different perspectives.

# A. TRUSTWORTHINESS OF INTEGRATED CIRCUITS FROM DIFFERENT PERSPECTIVES

Specialists who typically work independently on the main aspects of IC development: functional development, reliability, security, and functional safety, will have a different understanding of IC trustworthiness.

TABLE 1. Definition of characteristics of trustworthiness of a system.

| Trustworthiness characteristic | Description                                                                                                                                                                                                                |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Accountability                 | "State of being answerable for actions, decisions, and performance"                                                                                                                                                        |

| Accuracy                       | "Measure of closeness of results of observations, computations, or estimates to the true values or the values accepted as being true"                                                                                      |

| Authenticity                   | "Property that an entity is what it claims to be"                                                                                                                                                                          |

| Availability                   | "Property of being accessible and usable on demand by an autho-<br>rized entity"                                                                                                                                           |

| Controllability                | "Property of a system that allows a human or another external agent to intervene in the system's functioning"                                                                                                              |

| Integrity                      | System integrity: "Property of accuracy and completeness" Data integrity: "Property whereby data have not been altered in an unauthorized manner since they were created, transmitted, or stored"                          |

| Privacy                        | "Freedom from intrusion into the private life or affairs of an individual"                                                                                                                                                 |

| Quality                        | "Degree to which a set of inherent characteristics of an object fulfills requirements"                                                                                                                                     |

| Reliability                    | "Ability of an item to perform as required, without failure, for a given time interval, under given conditions"                                                                                                            |

| Resilience                     | "Capability of a system to maintain its functions and structure in<br>the face of internal and external change, and to degrade gracefully<br>when this is necessary"                                                       |

| Robustness                     | "Ability of a system to maintain its level of performance under a variety of circumstances"                                                                                                                                |

| Safety                         | "Property of a system such that it does not, under defined condi-<br>tions, lead to a state in which human life, health, property, or the<br>environment is endangered"                                                    |

| Security                       | System security: "Resistance to intentional unauthorized acts de-<br>signed to cause harm or damage to a system"<br>Information security: "Preservation of confidentiality, integrity,<br>and availability of information" |

| Transparency                   | "Property of a system or process to imply openness and accountability"                                                                                                                                                     |

| Usability                      | "Extent to which a system product or service can be used by speci-<br>fied users to achieve specified goals with effectiveness, efficiency,<br>and satisfaction in a specified context of use"                             |

(a) Trustworthiness characteristics taken from "Trustworthiness Vocabulary" in ISO/TS 5723:2022 [19]

| Maintainability | "the probability that the system can be successfully restored to operation after failure" [20]   |

|-----------------|--------------------------------------------------------------------------------------------------|

| Serviceability  | "relates to the time it takes to restore a system to service following<br>a system failure" [21] |

| Repairability   | "reflects the extent to which the system can be repaired in the event of a failure" [22]         |

| Confidentiality | "protecting information from unauthorized access" [23]                                           |

(b) Additional characteristics relevant for electronic systems

# 1) FROM THE PERSPECTIVE OF AN IC DESIGNER AND VERIFICATION ENGINEER

The goal of design and verification engineers is to ensure that requirement-fulfilling specification is implemented and that the IC function is complete and accurate. Furthermore, the design must be thoroughly verified and validated pre-silicon, as well as tested during manufacturing. This ensures that the IC behaves as expected under various operating conditions. In addition, meeting PPA requirements is essential. Thus, a trustworthy IC must not only correctly execute its functionality, but also strike a balance between power consumption, performance, and area utilization.

#### 2) FROM THE PERSPECTIVE OF AN IC RELIABILITY ENGINEER

The goal of a reliability engineer is to ensure that the IC should function as expected without any failures during its lifecycle. This applies not only in the presence of random faults due to external sources, e.g., radiation, but also under the effects of silicon wear-out, e.g., due to aging. Therefore, it is necessary for a trustworthy IC to ensure the absence

of failures by applying measures throughout its lifecycle, including design, manufacturing, and in-field.

### 3) FROM THE PERSPECTIVE OF AN IC SECURITY ENGINEER

The goal of a security engineer is to implement resilient measures to protect the IC against potential security threats, such as fault injection [25], insertion of hardware Trojans [26]. Therefore, security designers and architects prioritize security threats and implement adequate countermeasures. They have gone beyond the trusted anchor paradigm and have adopted the concept of zero-trust security model *never trust, always verify* [27] from network level to hardware level [28]. Therefore, a trustworthy IC requires not only a trusted anchor, but verification and validation focused on security.

# 4) FROM THE PERSPECTIVE OF AN IC FUNCTIONAL SAFETY ENGINEER

The goal of a functional safety engineer is to ensure that failures in the IC do not negatively impact the safe operation of the system in which it is integrated. To be considered functionally safe and to avoid potential legal exposure in the case of catastrophic events, ICs should be developed in accordance with the applicable functional safety standards of the industry in which the IC will be used. Thus, a trustworthy IC does not cause harm during operation in the event of failure, regardless of whether the failure is the result of functional errors or reliability-driven faults.

## 5) INDUSTRY STANDARDS AND GUIDELINES

To align efforts and establish a common level of expectation and interoperability between the different parties involved in each specific IC development aspects, many standards and guidelines have been developed covering the various aspects. Examples of common industry standards and guidelines that apply to IC development are detailed in Table 2.

#### **B. MOTIVATION AND PAPER CONTRIBUTION**

Due to the various perspectives described above, having a unified domain called trustworthy ICs leads to greater readiness to deal with emerging challenges. Therefore, trustworthiness at ICs level requires a compact definition with main overarching attributes. This would enable developers from different fields, who may have narrow field-specific perspectives on trustworthiness, to gain a better understanding of how trustworthiness impacts IC development overall. In this paper, we identify the minimum number of attributes required for the concept of trustworthiness at IC level. In addition, we elaborate on some of the most critical issues, spanning the various attributes, which should be addressed to achieve trustworthiness. Each issue is described in a consistent manner, focusing on the impact it has on trustworthiness and on existing and emerging countermeasures. The contributions can be listed as follows.

**TABLE 2.** Common industry standards and guidelines relevant for the discussed aspects of IC development.

| Development<br>Aspect | Standard or Guideline                                | Reference |

|-----------------------|------------------------------------------------------|-----------|

|                       | SystemC                                              | [29]      |

| Functionality         | Unified Power Format (UPF)                           | [30]      |

| and                   | Universal Verification Methodology (UVM)             | [31]      |

| Performance           | IP-XACT                                              | [32]      |

|                       | Portable Test and Stimulus Standard (PSS)            | [33]      |

|                       | AEC-Q100 Failure Mechanism Based Stress Test         | [34]      |

|                       | Qualification For Integrated Circuits                |           |

|                       | AEC-Q004 Automotive Zero Defects Framework           | [35]      |

| Reliability           | SAE J1879 Handbook for Robustness Validation of      | [36]      |

| Renability            | Semiconductor Devices in Automotive Applications     |           |

|                       | IEC 61709:2017 Electric Components - Reliability -   | [37]      |

|                       | Reference Conditions For Failure Rates And Stress    |           |

|                       | Models For Conversion                                |           |

|                       | ISO/SAE 21434:2021 - Road Vehicles - Cybersecurity   | [38]      |

|                       | Engineering                                          |           |

|                       | ISO/IEC 15408:2022 - Information Security,           | [39]      |

|                       | Cybersecurity and Privacy Protection                 |           |

|                       | IEC 62443 Industrial Communication Networks -        | [40]      |

| Canada                | Network and System Security                          |           |

| Security              | ISO/IEC 19790:2012 - Information Technology -        | [41]      |

|                       | Security Techniques- Security Requirements for       |           |

|                       | Cryptographic Modules                                |           |

|                       | IP Security Assurance - Security Annotation for      | [42]      |

|                       | Electronic Design Integration (SA-EDI)               |           |

|                       | IEC 61508:2010 Functional Safety of                  | [43]      |

|                       | Electrical/Electronic/Programmable Electronic        | -         |

|                       | Safety-related Systems                               |           |

|                       | ISO 26262:2018 - Road Vehicles - Functional Safety   | [44]      |

|                       | IEC 61511:2016 Functional Safety - Safety            | [45]      |

| Functional            | Instrumented Systems for the Process Industry Sector |           |

| Safety                | IEC 61513:2011 Nuclear Power Plants -                | [46]      |

|                       | Instrumentation and Control Important to Safety      |           |

|                       | IEC 62061:2021 Safety of Machinery - Functional      | [47]      |

|                       | Safety of Safety-related Control Systems             |           |

|                       | DO-254/ED-80 Design Assurance Guidance for           | [48]      |

|                       | Airborne Electronic Hardware                         |           |

- We provide a compact definition of trustworthy ICs focusing on four main attributes.

- We discuss the various impairments to trustworthiness attributes and their interactions.

- We investigate critical pre-silicon issues that can negatively impact the defined trustworthiness attributes and present them in a consistent way.

- We provide an overview of several existing methodologies for evaluating trustworthiness attributes.

Instead of proposing a new taxonomy that lists and classifies all potential trustworthiness issues, in this paper, we focus on selected issues that have a critical impact on the trustworthiness attributes and hold particular practical significance. The presented issues are classes of issues gathered from discussions with IC architects, designers, and verification engineers within the scope of the VE-VIDES project for trustworthy electronics [49]. The advantage of presenting the issues in such classes is that it provides an overview from a practical perspective along the pre-silicon stages of IC development.

Throughout this paper, we consider various sources, including academic literature, standards, industry experts' opinions, and industry-relevant publications, such as white papers. To the best of our knowledge, this is the first attempt to define trustworthiness in the context of ICs, by focusing on how it affects the various different development perspectives.

#### C. PAPER ORGANIZATION

The remainder of this paper is organized as follows. In Section II, we elaborate on the main attributes of trustworthy ICs and explain the various related impairments and their interactions. In Section III, we describe critical issues that can negatively impact the trustworthiness of ICs. We focus on elaborating what the issue is, how, where and by whom the issue is caused, how it impacts trustworthiness, and what countermeasures can be taken to counteract it. In Section IV, we provide an overview of several existing methodologies for evaluating the specific attributes of trustworthy ICs. In Section V, we conclude and highlight the need for a unified evaluation framework for trustworthiness of ICs.

# II. TRUSTWORTHY INTEGRATED CIRCUITS: ATTRIBUTES AND IMPAIRMENTS

To be able to elaborate on critical issues that negatively impact trustworthiness of ICs, it is essential to define trustworthiness in the context of ICs, as well as to identify its main attributes. Furthermore, it is important to understand the potential impairments to those attributes and the interactions between them.

# A. TRUSTWORTHINESS ATTRIBUTES FOR INTEGRATED CIRCUITS

The trustworthiness of a system encompasses a set of characteristics or attributes, as described in Table 1. This can be extended or reduced depending on the type of system, its application, and the industry in which it is applied. Since an IC is considered a subsystem within an electronic system, its trustworthiness is a prerequisite for the trustworthiness of the entire system. Although, as discussed above, various attributes are related to trustworthiness, there can be a hierarchical relationship between these attributes, as many of the attributes shown in Table 1 can be assigned as subattributes of others.

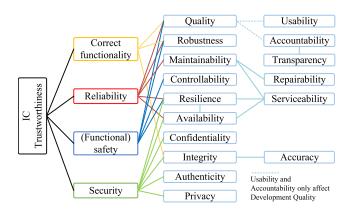

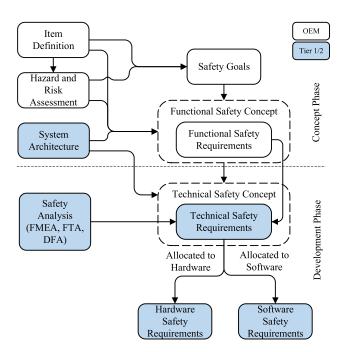

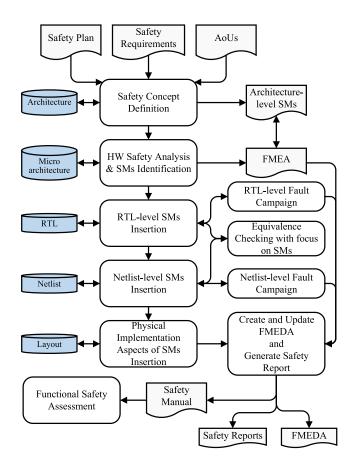

Our goal is to establish the minimum number of attributes required to address the various challenges faced during IC lifecycle as a result of emerging applications. Any definition of IC trustworthiness should enable the main development teams, which work independently of each other, to have a holistic understanding of the arising challenges. Motivated by this, we consider the following four as the main IC trustworthiness attributes: (1) correct functionality, (2) reliability, (3) security, and (4) safety, as they reflect the main aspects of development. The other attributes in Table 1 can be assigned as subattributes of these four, as shown in Fig. 2.

The **correct functionality** of an IC is the ability of the IC to execute the intended functionality and only the intended functionality. Per ISO/IEC TS 5723:2022 [19], the system trustworthiness must "*meet expectations in a verifiable way*". This places the burden on the subsystems, which in the case of electronics is an ICs, to fulfill their functionality correctly. Thus, the attribute of correct IC functionality is a minimum requirement for trustworthiness. Furthermore,

FIGURE 2. Attributes and subattributes of trustworthy ICs.

functionality must be verifiable, which makes it necessary to have a sufficient level of *development quality* that can assign *accountability* within the developing entity through *transparency* during development. The attribute of *usability*, at system level, is defined as the "extent to which a system can be used to achieve specified goals with effectiveness, efficiency, and satisfaction" [19], which is only possible if the functionality is implemented correctly at IC level. In addition, a correct function must be complete and accuracy, thus covering the subattributes of *integrity* and *accuracy*. Lastly, *robustness*, which is concerned with maintaining the level of performance, is also necessary for the IC to perform the functionality correctly under varying circumstances.

The **reliability** of an IC is the ability of the IC to perform its functionality over its lifetime without failures. This covers the subattributes of *robustness*, which requires that an IC maintains its level of performance; and *resilience*, which is related to the ability of the IC to maintain its functionality regardless of internal or external changes, e.g., faults. A prerequisite of reliability in the context of ICs is *semiconductor quality*, which is concerned with early-life failures. A certain *availability* of the IC is necessary to consider it reliable. *Maintainability*, which is concerned with the probability that the system will be restored after failure, is affected by other subattributes, such as *repairability*, concerned with the extent of restoration, and *serviceability*, concerned with the restoration time. In addition, *serviceability* and *repeatability* impact several other subattributes, as shown in Fig. 2.

Safety is "the freedom from unacceptable risk of physical injury" [50]. In systems, such as electronic ones, when it is possible to take countermeasures to ensure that the function does not cause safety-related issues, the concept of functional safety becomes relevant. Functional safety is concerned with the safe functioning of a system; more specifically, "freedom from unacceptable risk of injury or damage to people's health by properly implementing one or more automatic protection functions" [43]. Therefore, functional safety is considered a main attribute of trustworthiness in the context of ICs, as it becomes especially relevant for safety-critical industries, such as automotive, medical, and

aerospace, where significant effort is spent, up to 60% increase [51], to ensure the functional safety of ICs. For an IC to be functionally safe, it must cover the already discussed subattributes of *development and semiconductor quality*, to address systematic and random faults; as well as *robustness*, and *resilience*. Finally, functional safety covers the subattribute of *controllability*, which is concerned with whether sufficient measures are taken so that external parties can control the impacts of a failure when necessary to maintain safety.

The **security** of an IC is the protection of the IC from unauthorized access, manipulation, or any form of malicious interference that could compromise its functionality or the confidentiality of the data it handles. A secure IC must exhibit the properties of the subattributes of *confidentiality*, *integrity*, and availability (CIA), as well as provide privacy for the data handled by the IC. The subattribute of *confidentiality*, in the context of IC development, is not only concerned with data but also with the *confidentiality* of associated IP, e.g., design information. Availability, in the context of data, is also a related subattribute. Finally, a secure IC must exhibit resilience against attacks.

# **B. IMPAIRMENTS TO THE TRUSTWORTHINESS OF INTEGRATED CIRCUITS**

To ensure trustworthiness, it is necessary to understand its impairments. Since IC trustworthiness encompasses multiple attributes, many impairments can negatively affect it; they can be classified as *systematic* faults, *random* faults, and *intentional* faults.

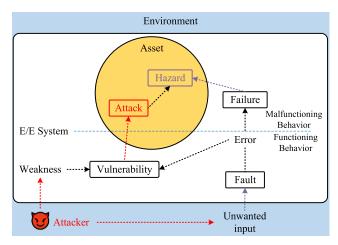

A **fault** is an abnormal condition that, when activated, can cause an **error**, which, when propagated, can lead to a failure [44]. A **failure** is defined as the loss of ability to perform a function as required [44].

A systematic failure is the result of deterministic systematic faults such as lack of systematicity during development, i.e., not following systematic approaches correctly, resulting in design mistakes. Systematic faults can also lead to security weaknesses, such as side-channel information leakage, which can be exploited later by malicious parties. This type of failure can only be prevented by applying process or design measures.

Random faults are faults that are probabilistic in nature and arise from many sources, e.g., radiation, process variation, temperature, electromagnetic interference, and transistor aging [44]. They can be classified into transient and permanent faults. Random faults can lead to random failure due to two types of errors: soft and hard errors. Soft errors, due to transient faults, have a transient effect on the semiconductor device that disappears by itself after some time, while hard errors, due to permanent faults, have a permanent effect that lasts indefinitely if not repaired. Soft errors are mainly the result of Single-Event Effects (SEEs) caused by particle radiation, e.g., cosmic rays and alpha particles, categorized mainly as Single-Event Upset (SEU)

and Single-Event Transient (SET), depending on their effect on silicon. While SEU induces bit-flips in memory cells states directly, SET affects combinational logic causing transient voltage disturbance that can manifest as SEU in sequential elements if successfully propagated and latched, thus not electrically, logically, and temporarily masked. On the other hand, hard errors are permanent transistor damages that have different forms, e.g., stuck-at-0, stuck-at-1, or bridging faults, which are shorts between two signal lines. Permanent faults arise due to many reasons, including manufacturing defects, transistor aging effects, such as electromigration, strong radiation, and systematic faults during design [52], [53], [54].

Finally, **intentional faults** are faults introduced by a malicious entity to carry out an attack. Such faults can be active, in cases where normal operation is disrupted, or passive, in cases where inherit properties of the semiconductor are exploited.

# 1) HOW IMPAIRMENTS AFFECT TRUSTWORTHINESS ATTRIBUTES

In the following, we explain how the aforementioned main attributes of trustworthy ICs can be affected by the described impairments.

- The correct functionality of an IC can be negatively affected by various factors: (1) design and production mistakes (systematic faults), (2) random radiation-induced events leading to silicon faults (random faults), and (3) malicious influences, such as the insertion of Trojan circuits (intentional faults), which can violate the correct operation of an IC.

- The reliability of an IC is mainly affected by random failures that occur due to random faults, e.g., SEUs. Furthermore, reliability can be affected by early wearout (systematic fault) in cases where reliability is not considered properly during development.

- The security of an IC is affected primarily by intentional faults. Furthermore, systematic faults, e.g., the lack of countermeasures implemented in the design, can be exploited to affect security. However, random faults are usually not relevant for security, unless they impact the functionality of parts of the IC responsible for the security functions, such as the root of trust or the Advanced Encryption Standard (AES) cipher.

- The functional safety of an IC is affected by systematic and random faults, which can lead to failures that negatively affect the safety-relevant functions, leading to violations of safety goals [44].

In summary, while systematic faults are the main impairment to correct functionality of ICs, random faults are primarily a reliability issue, which can eventually also negatively affect correct functionality. Both systematic and random faults need to be addressed to achieve functional safety, while intentional faults are the main concern for security.

#### C. INTERACTION BETWEEN DIFFERENT IMPAIRMENTS

Although we have already described the main attributes and impairments, there are additional terms that should be elaborated to understand trustworthiness and analyze the various issues that negatively impact it. In this section, we will elaborate on those terms and indicate how they interact with each other.

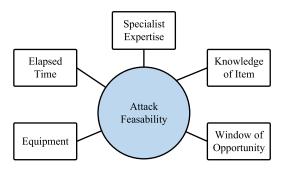

Threat describes the potential of an adversary to launch and execute an attack. A threat is closely related to two concepts. The first is vulnerability of the IC, which can be introduced by exploiting certain weaknesses. Weaknesses are hardware conditions that arise due to flaws in different development stages and that can compromise the CIA of the IC. The second is the **asset**, which represents something of value to a stakeholder, e.g., secret keys or IP details. Due to the existence of vulnerabilities, an asset is exposed to threats. Successful exploitation of a vulnerability is termed **exposure**. Attackers are malicious threat sources that carry out attacks, i.e., the action of exploiting a vulnerability to damage an asset. A vulnerable IC might be susceptible to specific threat scenarios. Still, these only become relevant with a worthwhile asset at the center of attention, i.e., an appropriate motivation for the attacker to exploit a vulnerability and let the threat scenario become a reality. Examples of threats include: fault injection attacks, which deliberately introduce faults in the hardware under attack, e.g., by means of voltage glitches or high-energy beams [24], to alter the behavior of the target IC; exploitation of architectural faults [24], e.g., the Rowhammer method [55]; hardware Trojans, which can be inserted through an untrustworthy manufacturing chain, potentially spanning poisoned Register-Transfer Level (RTL)-level library elements, untrustworthy design software, to untrustworthy manufacturing; IP piracy and counterfeiting; and reverse engineering.

**Hazard** is a potential source of harm caused by the system to the system user, as a result of an IC function deviation, **malfunctioning behavior**. This malfunctioning behavior could be the result of a random or deterministic failure, inappropriate performance, or an attack. While hazards arising from systematic failures can be counteracted by systematic development approaches; the identification and control of hazards that emerge from random hardware failures, and the mitigation of their effects, can be achieved using Safety Mechanisms (SMs).

**Risk** is a measure of the probability that a hazard or threat becomes an issue for the trustworthiness of an IC. In the context of security, risk is the probability of losing an asset, which is higher when there are numerous vulnerabilities and there is increased attacker capability. In the context of functional safety, risk is the probability that a hazard leads to harm. Overall, risk indicates the probability and severity level of hazard or threat. Therefore, risk is relevant to threats, hazards, and assets.

Considering trustworthiness as a whole is important because of the dependencies and interactions that the various development aspects have with each other. For example,

FIGURE 3. Interaction between impairments.

a safety-critical IC used in an autonomous vehicle is also a security-critical one, but considering each aspect separately is not sufficient to achieve trustworthiness, as there is a link between hazards and threats. While hazard is more general and highly related to the system asset, threat reflects the risk of exploiting a vulnerability by an attacker to violate or harm the system asset. Fig. 3 illustrates the links between threat, hazard, and asset. Fundamentally, a threat may lead to a hazard in a safety-critical system, specifically when an attack affects safety goals. However, while a hazard does not pose a threat to security-critical systems, a fault can be exploited to create a vulnerability. Understanding the interaction between these impairments is crucial to achieve trustworthy ICs.

# III. ISSUES TO THE TRUSTWORTHINESS OF INTEGRATED CIRCUITS AND THEIR IMPACT

With the fragmentation of the supply chain of ICs, ensuring the trustworthiness of each IC development stage becomes increasingly difficult, especially since various issues can negatively affect it. These issues are not only of various categories but also appear in various stages of the ICs development cycle.

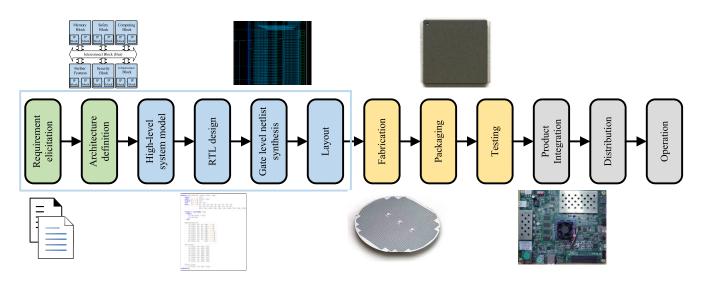

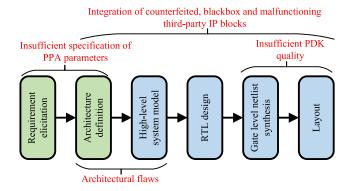

Developing an IC typically starts with requirements and architecture definition, followed by front- and back-end implementation stages, and ends with the fabrication, packaging and testing stages, before being integrated into a product. A simplified model of the development cycle of an IC is shown in Fig. 4. In this paper, we focus on the issues that appear during the specification, architecture, and design stages; in other words, we focus on the pre-silicon issues to IC trustworthiness. These stages are bordered in light blue in Fig. 4.

In Section II we discussed impairments to trustworthiness attributes. There can be various causes that can appear throughout the IC development flow for these impairments. In this paper, we use the term *issue* to refer to these potential causes of IC trustworthiness impairments. The described issues are grouped in such a way as to reflect the main

FIGURE 4. Typical IC development flow. The light blue line indicates the pre-silicon stages that are the focus of the paper.

**TABLE 3.** Criteria used to consistently describe issues to trustworthiness of ICs.

| Criteria              | Description                                                                         |

|-----------------------|-------------------------------------------------------------------------------------|

|                       | Specifies whether the issue is internal or external with respect to IC development. |

| Internal/External     | Internal: the issue originates from within development (e.g.,                       |

| mternal/External      | hardware architect, IC designer, verification engineer)                             |

|                       | External: the issue targets the development from outside                            |

|                       | (e.g., foundry, hacker, third-party IP vendor)                                      |

| Source                | Identifies the source of the issue. This can be, for example,                       |

| Source                | a malicious employee, a third-party IP vendor, a hacker, etc.                       |

| Stage of introduction | Specifies the stage(s) where the issue is introduced.                               |

| Outcome(s)            | Specifies the potential outcome(s) from the impact of the                           |

| Outcome(s)            | issues.                                                                             |

| Countarmacoura(a)     | Describes potential existing or emerging countermeasures to                         |

| Countermeasure(s)     | counteract the negative impacts of the issue.                                       |

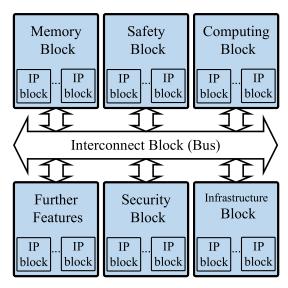

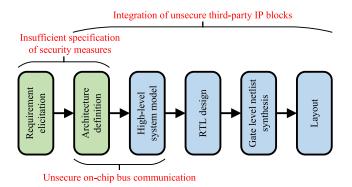

attributes of trustworthiness, i.e., correct functionality, reliability, security, and functional safety. Since modern complex ICs, such as System-on-Chips (SoCs), are increasingly more dependent on externally developed third-party IP blocks, the issues that arise from their integration are treated as a separate group. The same applies to hardware Trojans, which require a dedicated focus due to their high potential for negative impact.

We describe each issue in detail, focusing on describing the issue, its impact on IC trustworthiness, and existing and emerging solutions and countermeasures. Table 3 shows the aspects that we consider when describing an issue.

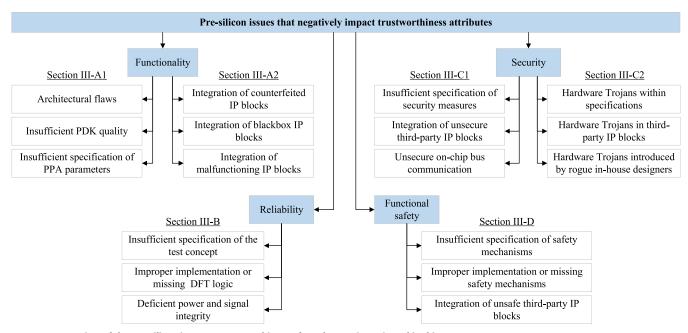

To facilitate an easier reading of the paper, Fig. 5 provides an overview of the organization of Section III. Section III-A discusses issues related to the correct functionality of ICs, where Subsection III-A1 focuses on general functionality issues, while Subsection III-A2 focuses on issues associated with the integration of third-party IP blocks with relevance to functionality. Section III-B discusses reliability issues. Section III-C discusses security issues, where Subsection III-C1 focuses on general security issues, while Subsection III-C2

focuses on hardware Trojans. Finally, Section III-D discusses functional safety issues.

#### A. ISSUES IMPACTING CORRECT FUNCTIONALITY

In this subsection, we primarily confine ourselves to issues that negatively affect correct ICs functionality. The stages in which these issues occur are depicted in Fig. 6; where it can be seen that issues with architecture, Process Design Kit (PDK) quality, and specification of PPA parameters appear in the earlier stages of development, while those arising due to the integration of third-party IP blocks can occur at any stage, depending on the stage of the IP integration.

### 1) GENERAL FUNCTIONALITY ISSUES

In the following, we focus on specification-related issues appearing during the requirement elicitation and architecture definition stages that impact correct functionality of an IC. Specifically, we look at the issues caused as a result of: a flawed architecture, insufficient PDK quality, and insufficient specification of PPA parameters.

### ARCHITECTURAL FLAWS

Description: The architecture of an IC is developed based on technical requirements during the architecture definition stage. The more complex ICs, such as SoCs, are generally composed of various IP blocks, also known as IP cores, or IPs for short, which are purchased from multiple IP vendors. In such an IP-based IC design methodology, the architecture definition stage becomes more important. The main advantage of following this methodology is that design houses focus on the design of innovative, stable, and efficient IC architectures and avoid the introduction of architectural flaws, which are systematic faults during architectural design, such as improper performance budgeting or the selection of unsuitable IP blocks. The main challenge with conventional

FIGURE 5. Overview of the pre-silicon issues to trustworthiness of ICs that are investigated in this paper.

FIGURE 6. Investigated issues that affect the correct functionality of ICs.

IC architectural design is that it is a manual process that depends mainly on the skills and experience of the IC architecture team, especially when choosing appropriate IP blocks. After arriving at a suitable high-level architecture that should already fulfill the defined requirements, it is important to validate the proposed architecture against PPA requirements and other Key Performance Indicators (KPIs) by applying a virtual prototyping-based architectural analysis [56]. This process is often referred to as architectural exploration, since multiple architectures may be explored. KPI validation continues with RTL emulation, Field Programmable Gate Array (FPGA) prototyping, and ends with post-silicon testing on testers. This issue is internal to the development of the IC and can be caused by hardware architects. If not detected, the flaws may persist in the IC during deployment.

Impact on IC trustworthiness: Architectural flaws can jeopardize the functionality, performance, security, and functional safety of the IC. In fact, cost-intensive re-spins,

such as the redesign of ICs after tape-out, are often the result of bugs that are found very late in the development cycle, e.g., during testing or prototyping [57].

Countermeasures: In order to avoid this issue, it is important to follow a systematic design approach and sufficient validation steps. For example, during the architecture design and verification stages, many aspects need to be carefully considered, as they have major implications on the functionality and performance of the IC. This includes hardware/software partitioning, the selection of Central Processing Unit (CPU), Graphics Processing Unit (GPU), Digital Signal Processing (DSP) cores and hardware accelerators, the size and type of memory, the type and bandwidth of on-chip interconnect, and the selection of interfaces, Input/Output (I/O) ports, and other IP blocks [56].

To arrive at a trustworthy IC architecture, it is imperative to verify the fulfillment of not only functional requirements, but also defined trustworthiness requirements. Among others, the architectures of ICs for security-critical and safety-critical applications should include dedicated components to ensure security and functional safety, such as the hardware root of trust modules [58], [59], used to provision security-critical functions, and a dedicated safety island, used to manage and monitor safety-relevant operations within the IC, as in [58] and [59]. With respect to reliability, it is vital that an appropriate process technology node that meets the failure rate requirements is selected. Similarly, appropriate IP blocks should be selected to meet reliability requirements.

Research projects invest in the establishment of standardized IC architectures to ensure trustworthiness and reduce effort at the same time. Da Silva et al. [60] have described an industry-based list of shared features for automotive SoC architectures, i.e., safety-related components,

application-specific units, automotive protocols, and security cores, and have implemented these features in an open source SoC benchmark, AutoSoC, where the notion of functional blocks is key to maintaining a modular design. Various iterations of AutoSoC have the ability to employ a variety of hardware components to meet the specific requirements of each functional block [60]. With a focus on security, there are also special standardized security architectures, e.g., ARM Trustzone [61], which establishes a Trusted Execution Environment (TEE) as an isolated part of the architecture.

#### INSUFFICIENT PDK QUALITY

Description: While avoiding issues with architecture definition is important, it is not sufficient if the implementation uses an insufficiently qualitative PDK. With decreasing technology node sizes and the potential usage of various technologies in a single design, such as in chiplets, PDKs get increasingly more important, while at the same time becoming more difficult to verify and synchronize, and more expensive to develop [62]. This is an external issue from the perspective of the IC developers, since PDKs are provided by the foundries.

A PDK is a set of documentation and data files that describes a fabrication process in a semiconductor foundry and enables the user to complete a design. A typical PDK contains technology files, cell libraries with models and parametric cells (pcells), rule files, verification checks, and reference flows [63], [64]. PDKs usually contains proprietary information from the foundry and trade secrets and are not always fully transparent.

Impact on IC trustworthiness: The difficulty of resolving issues that arise as a result of an insufficiently qualitative PDK increases due to the proprietary nature of PDKs. An insufficiently qualitative PDK can lead to incorrect functionality, performance and yield issues, and costly and time-consuming redesign effort.

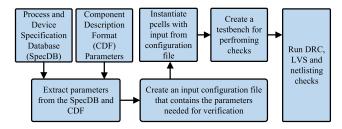

Countermeasures: Conducting review measures during the design stages, e.g., verifying current and voltage ratings, and comparing the measured data with the provided models within the PDK, may mitigate this issue [65]. However, to decrease the burden and expenditure of the IC developer, measures undertaken during PDK development are preferred. Methodologies for PDK Quality Assurance (QA) and integrity are described in literature [66], [67] and implemented in industry [68]. For example, Global Semiconductor Alliance (GSA) has developed a checklist for PDK quality for analog/mixed signal PDKs [68]. Projects are underway, including publicly funded projects [49], to develop trustworthy PDKs. XFab, for example, has introduced an automated PDK verification flow, XVerifFlow [69], the main stages of which are shown in Fig. 7. This enables verification of various parameters of pcells, while considering parameters extracted from a specification database and Component Description Format (CDF). Furthermore, XverifFlow can be used to review netlisting procedures, device extraction, and post-layout simulation.

FIGURE 7. The key stages in XVerifFlow PDK verification flow adapted from [69].

#### INSUFFICIENT SPECIFICATION OF PPA PARAMETERS

Description: One of the main design goals is to achieve high performance at low power consumption on a small area. However, achieving this is not trivial, especially as new applications require lower area while also demanding lower power for higher performance. When considering the aim of lowering costs and increasing IC complexity, the task of PPA optimization becomes even more complex. In addition, PPA optimization can introduce bottlenecks in various aspects of the system, affecting other aspects, such as constraining the choice of technology node, IP blocks, and interconnect solutions [70]. Furthermore, the lack of accurate models, e.g., for memory utilization [70], [71], can have a significant negative impact on PPA. This is an issue that is internal from the perspective of the IC developers and can be caused by requirement engineers or hardware architects.

Impact on IC trustworthiness: Incorrect assumptions about the required power and performance can result in inadequate or faulty functionality, e.g., due to timing violations in critical paths that manifest themselves in later physical implementation stages.

Countermeasures: To address this issue, it is important to start the PPA-oriented design and verification as early as possible in the development lifecycle, also known as shift-left strategy. One such approach is to move the level of abstraction to modeling, e.g., SystemC, to allow faster development of efficient IC architectures for the target PPA [72]. This can be achieved by using virtual prototyping and architectural modeling to validate the proposed architecture against PPA requirements pre-RTL. These approaches, such as [73] and [74], can also applied to evaluate the security of ICs. Furthermore, RTL power analysis should be considered, and power validation is to be performed at later stages on the gate-level netlist and final layout. In a template-based IC design, customizing precise PPA prediction methods is essential. Tang et al. [75] propose a fast and precise PPA prediction method for template-based processor design. Furthermore, Electronic Design Automation (EDA) vendors have moved to solutions that provide faster design-space optimization and apply Artificial Intelligence (AI) [76], [77], [78]. The main idea is to learn from various design implementations and to explore various PPA combinations in parallel to find the optimum solution. For example, prior learning can vastly improve the lowest power required to

FIGURE 8. A simplified block diagram of an IC designed with the IP-based design methodology.

maintain a low Total Negative Slack (TNS) over an expert's best manual result [77].

Table 4 summarizes the general issues that affect the correct functionality of ICs.

# 2) ISSUES SPECIFIC TO THE INTEGRATION OF THIRD-PARTY IP BLOCKS

The integration of semiconductor IP blocks for the development of ICs has gained more adoption in recent years and has become common practice in the semiconductor industry [79], [80]. According to estimates from 2017, 75% to 80% of computer ICs included IP blocks from thirdparty vendors, which increased from 50% in 2013 [81]. Following this IP-based IC design methodology, a number of pre-designed blocks (i.e., processors, accelerators, memories, I/O ports and peripheral interfaces, interconnects, Analogto-Digital Converter (ADC) and Digital-to-Analog Converter (DAC), etc.) are integrated to reduce development cost and effort for new ICs, accelerate their development, and shorten their time-to-market [79], [82]. Such IP blocks are reusable, highly optimized, verified, and, if required for the target application, they are qualified for reliability or pre-certified for functional safety; most importantly, they are easy to integrate and configure. Due to their modularity and because they are usually deployed in previous ICs, IP integrators - a term used to describe IC design houses whose main focus is the selection, correct configuration, and integration of the purchased IP blocks to an IC, instead of the design and implementation of specific logic blocks - have more confidence in their correct functionality and assume them to be trustworthy. In addition to purchasing IP blocks from thirdparty IP vendors, IP blocks may be developed in-house. Fig. 8 shows a simple block diagram of an IC developed with the IPbased IC design methodology.

IP blocks can be digital, analog or mixed signal and belong to different abstraction levels, e.g., RTL (soft IPs), gate level, as a netlist (firm IPs), or layout level, in GDSII format (hard IPs) [79]. In particular, IP blocks based on standards, e.g., the Universal Serial Bus (USB) mixed-signal IP block is built following the specification of USB Implementer Forum [83], are often purchased from specialized third-party vendors. This is because such IP blocks are developed according to industry standards specifications, and developing them in-house does not provide a competitive advantage to the IP integrator. In addition, there is an increasing number of open source IPs, e.g., RISC-V cores, which are provided by the community free of licensing fees in communities, e.g., OpenCores [84] and GitHub.

In addition to cost and performance, the trustworthiness of IP blocks is a major focus of IP integrators since IP blocks are the main building block of today's complex ICs, and a single untrusted IP can compromise the trustworthiness of the entire IC, as Munsey in [85] says "a single bad IP is all it takes to break your SoC".

In the following, we focus on three different issues that affect the trustworthiness of ICs, namely the integration of counterfeited, blackbox, and malfunctioning IP blocks. From the perspective of the IP integrator, these issues represent external threats, if the integrated IP blocks are purchased from external third-party IP vendors. If the integrated IP blocks are developed in-house, then these issues may be caused by in-house IP designers, and thus may be considered internal. However, since IP blocks are usually purchased from third-party IP vendors, we consider the three aforementioned issues as external issues.

As depicted in Fig. 6, these issues can appear anywhere along the design stages of the ICs, starting with architecture definition, as they depend on the stage at which the IP is integrated, e.g. RTL for soft IPs, and layout for hard IPs. The issues described in this subsection complement the issues *Integration of unsecure third-party IP blocks*, Hardware Trojans in third-party IP blocks, and Integration of unsafe third-party IP blocks, which are mapped to the other trustworthiness attributes in Section III-C1, Section III-C2, and Section III-D, respectively.

### INTEGRATION OF COUNTERFEITED IP BLOCKS

Description: The integration of counterfeited third-party IP blocks can have negative consequences for both the IP vendor and the IP integrator, depending on which party is acting maliciously. From the perspective of the IP vendor, the provided IP blocks may be extensively used by the IP integrator beyond what was agreed in the licensing agreement. This leads to the violation of the copyright of the IP vendor and to financial losses. Furthermore, the licensed IP block may be leaked or slightly modified, e.g., by adding or reducing features, without permission and then resold as a new IP block [79]. Since we focus on this paper on the impact on the trustworthiness of IC, we focus on this issue from the perspective of the IP integrator.

| Criteria              | Architectural flaws                                                                                                                                            | Insufficient PDK quality                                                                                                     | Insufficient specification of PPA parameters                                                                                                                   |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal / External   | Internal                                                                                                                                                       | External                                                                                                                     | Internal                                                                                                                                                       |

| Source                | Hardware architect                                                                                                                                             | Foundry                                                                                                                      | Requirements engineer<br>Hardware architect                                                                                                                    |

| Stage of introduction | Architecture definition                                                                                                                                        | Gate level netlist synthesis                                                                                                 | Requirement elicitation                                                                                                                                        |

| Stage of introduction | High-level system model                                                                                                                                        | Layout                                                                                                                       | Architecture definition                                                                                                                                        |

| Outcome(s)            | Jeopardized functionality, functional safety,<br>security, and performance<br>Cost-intensive respins                                                           | Jeopardized functionality, reliability,<br>performance and yield<br>Cost-intensive respins                                   | Inadequate or faulty functionality                                                                                                                             |

| Countermeasure(s)     | Use a systematic design approach Apply sufficient validation steps Use virtual prototyping-based architectural analysis Use special standardized architectures | Apply review measures during the design stages<br>Use PDK development checklists<br>Utilize automated PDK verification flows | Start PPA-oriented design and verification early Use virtual prototyping and architectural modeling Use Al to optimize the design space and achieve better PPA |

TABLE 4. Summary of general issues that affect the correct functionality of ICs.

Counterfeited IP blocks can be acquired by IP integrators in different forms, e.g., by illegally purchasing IP blocks, which are leaked by previous buyers, disloyal employees or hackers. Furthermore, the IP integrator may integrate unauthorized IP blocks, e.g., commercial usage of academic IP blocks, or use licensed IP blocks excessively. The latter is also known as IP overuse [86], [87], [88] and can lead to legal exposure and reputational damage to the IP vendor but does not negatively impact trustworthiness assuming the IP block has not been tampered with. Counterfeited IP blocks can result from IC cloning where malicious supply chain parties clone a design in transit or reverse engineer an IC after fabrication, leading to IP theft. This issue is often referred to as IP piracy [89], [90]. The effects of the integration of counterfeited IP blocks appear during operation and are persistent, as they cannot be remedied during field operation and require the re-designing of the IC.

Impact on IC trustworthiness: Integrating counterfeited IP blocks affects all trustworthiness attributes. This is because counterfeited IP blocks may suffer from systematic faults and include malicious modifications and backdoors, e.g., due to hardware Trojans, which can lead to compromised functionality or the violation of any trustworthiness attributes. Depending on the issue that the counterfeited IP block includes, negative effects may be inflicted on any trustworthiness attribute.

Countermeasures: To reduce the risk of exposure to this issue, design houses must qualify the IP blocks they integrate for authenticity and integrity. Furthermore, IP vendors should take measures to protect their IP blocks. For example, IP watermarking techniques [91], [92], which insert a unique identify that can be checked to prove the ownership of an IP, can be applied. In addition, logic locking [93] is an active measure that locks an IP block with a secret key. This key is only known to the IP vendor and legitimate IP integrators thus preventing unauthorized usage.

# INTEGRATION OF BLACKBOX IP BLOCKS

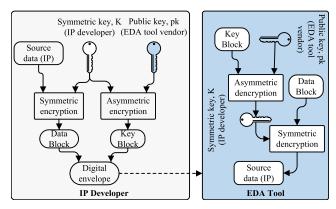

Description: It is in the interest of IP vendors to protect their copyrights to maintain a profitable business. Therefore, the IEEE has established the IEEE P1735 standard [94], which provides a unified encryption/decryption scheme and

FIGURE 9. Workflow of the IEEE P1735 standard [94].

rights management for IP blocks. In this way, encrypted soft IPs are protected from direct cloning or modification of the RTL source code, while exclusively allowing functional verification and synthesis using EDA tools [79], as described in Fig. 9. However, since the RTL source code, plain text RTL, of the IP blocks is not accessible, IP integrators are forced to integrate, verify and validate them as non-transparent "blackbox" excluding the possibility of conducting RTL reviews or RTL analysis. For example, many security and trust verification techniques in the literature [95], [96], [97] require access to the RTL source code [79].

The effects of this issue are evident during verification, and the negative consequences are persistent and appear during operation.

Impact on IC trustworthiness: For IP integrators, not being able to exercise arbitrary verification and analysis techniques is a major gap that raises concerns about the trustworthiness of encrypted soft IPs. For example, such IP blocks may include security vulnerabilities, such as hardware Trojans [26], [98], [99], [100], [101], [102], [103], or functional safety issues. Depending on the problem that the blackbox IP block causes, negative outcomes may affect all trustworthiness attributes.

Countermeasures: Novel techniques that enable trust assurance despite dealing with encrypted soft IPs are needed. For example, Mishra et al. [79] suggest focusing future research on gate-level verification and analysis techniques,

since gate-level netlists, synthesized from encrypted soft IPs, are usually not encrypted. On the other hand, IP vendors offer firm or hard IPs that are usually configurable, but mostly have an inaccessible inner architecture. This leads to similar negative effects as discussed for encrypted soft IPs. In addition, integrating encrypted netlists, while cheaper, presents additional place and route, simulation, and debug challenges.

To address the challenges that arise from the integration of third-party IP blocks, especially encrypted ones, interface agreements can be set up to address liability. For example, in the automotive industry, to manage the liability of the IP integrator and final customer of ICs, the Original Equipment Manufacturer (OEM), the industry often applies Design Interface Agreements (DIAs), which is a document that defines the responsibilities of all parties, where the OEM is concerned with the system, while the suppliers are concerned with the performance and functional safety of the components [104]. Nevertheless, such agreements could be expanded to include additional checks and requirements to help increase the trustworthiness of the provided third-party IP blocks, which would be a new form of DIA, the trustworthiness DIA.

#### INTEGRATION OF MALFUNCTIONING IP BLOCKS

Description: To save cost, IP integrators may purchase low-cost IP blocks with potentially bad quality and functional deficiencies, which fail under specific conditions, or include bugs in their functions [105], [106]. Such issues are very hard to uncover, since IP integrators may not have technical insights or access to the internals of the IP block, as discussed for blackbox IP blocks [105], [106]. This issue is particularly dangerous, because it may be unintentionally inflicted by IP vendors, assuming that the IP vendor is not acting maliciously. Therefore, IP integrators must not assume that commercial IP blocks are bug-free and should perform functional verification of IP blocks and validation at IC-level, in addition to analyzing the quality of the purchased IP blocks before integration.

Impact on IC trustworthiness: Integrating malfunctioning IP blocks, i.e., IP blocks that do not execute their functionality as specified, or have performance issues, has a major negative impact on the functionality of the IC, such as causing inadequate and faulty functionality, as well as all other trustworthiness attributes, depending on what kind of bug or deficiency they contain.

Countermeasures: It is the responsibility of the IP integrator to integrate only high-quality IP blocks that pass a strict selection and qualification process [57]. For example, IP blocks that provide proof of proper functionality and meet stringent quality criteria should be integrated. In addition, it is important to ensure that the IP vendors have traceable and documented development processes and offer certification for their processes and IP blocks, e.g., in automotive, at least ISO 9001 [107] and International Automotive Task

Force (IATF) 16949 [108] for quality, ISO 26262 [44] for functional safety, Automotive Electronics Council (AEC)-Q100 [34] for reliability qualification, ISO/Society of Automotive Engineers (SAE) 21434 for cybersecurity [38], and ISO 21448 [109] for safety of the intended functionality. Using only IP blocks that have been used previously in other ICs, can be a further criterion when integrating IP blocks in applications that require high levels of trustworthiness. However, this can have a negative impact by preventing innovation. Additionally, it is recommended to only integrate IP blocks from established IP vendors, or widely adopted open-source IP blocks since their correct functionality has been validated by the community. Finally, it is vital that the IP integrator avoids usage mistakes (1) by ensuring that the IP blocks are configured correctly and are integrated error-free; and (2) by performing IC-level validation as early as possible during development, because the later bugs are discovered, the higher the cost of fixing them [80].

Table 5 summarizes the issues related to the integration of third-party IP blocks that affect the correct functionality ICs.

#### B. ISSUES IMPACTING RELIABILITY

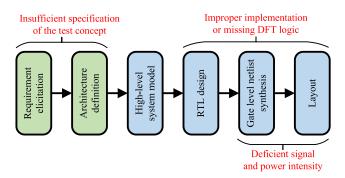

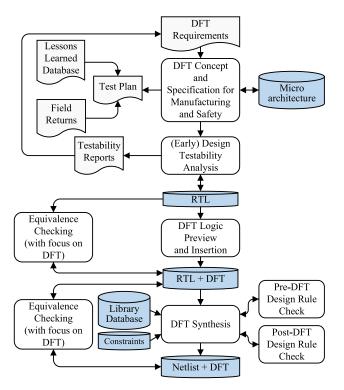

As discussed in Section II-A, reliability is an attribute of trustworthiness. Given the importance of testing to overcome issues with reliability, in this section, we focus on issues with negative impact on Design for Testability (DFT) and testing. In addition, we discuss the issue of deficient signal and power integrity, due to its impact on reliability.

DFT is an important design aspect in IC development because of the need to ensure the correct functionality and reliability of increasingly complex IC designs. In particular, in advanced technology nodes, manufacturing defects are more likely to occur, yield is lower, and semiconductors are more prone to reliability issues in the field, e.g., signal and power integrity or electromigration [110]. The goal of DFT is to allow testing during manufacturing and packaging to sort out defective dies and packaged ICs, respectively, and to enable testing during operation. Based on the test results, diagnostics and yield analysis can also be performed [111], [112], [113].

To enable the testing of ICs, DFT logic need to be inserted. For the testing of sequential elements, scan chains, which consist of a chain of flip-flops or latches that can serially shift in and out data are applied. Furthermore, Build-in Self Test (BIST) circuits, such as Logical Build-in Self Test (LBIST) and Memory Build-in Self Test (MBIST), are used during manufacturing tests and deployed during operation to monitor for permanent faults [110], [114].

DFT-related measures are involved in the different stages of IC design and manufacturing, thus issues can arise at all stages. Since the focus of this paper is on pre-silicon stages, we focus on two main issues related to DFT, i.e., the insufficient specification of the test concept, and improper implementation or missing DFT logic. In addition, we also look at the issue of deficient signal and power integrity. These

| Criteria              | Integration of counterfeited IP blocks                                                                                                 | Integration of blackbox IP blocks                                                           | Integration of malfunctioning IP blocks                                                                                                                                                                                                                                                                                                        |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal / External   | External                                                                                                                               | External                                                                                    | External                                                                                                                                                                                                                                                                                                                                       |

| Source                | Third-party IP vendor                                                                                                                  | Third-party IP vendor                                                                       | Third-party IP vendor                                                                                                                                                                                                                                                                                                                          |

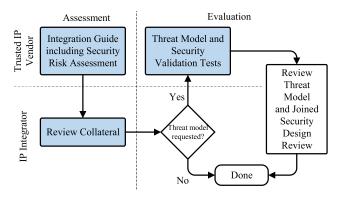

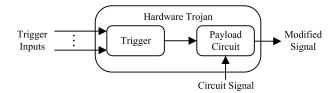

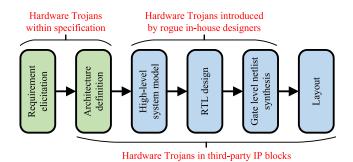

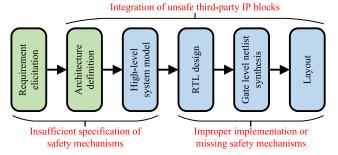

| Stage of introduction | Any, starting with Architecture definition                                                                                             | Any, starting with Architecture definition                                                  | Any, starting with Architecture definition                                                                                                                                                                                                                                                                                                     |