# Design of Highly Integrated Interface Electronics for Capacitive Micromachined Ultrasonic Transducers

## **Prajith Kumar Poongodan**

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik (EIT) der Universität der Bundeswehr München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs (Dr.-Ing.)**

genehmigten Dissertation.

#### Gutachter:

- 1. Prof. Dr. techn. Linus Maurer

- 2. Prof. Dr.-Ing. Ralf Brederlow

Die Dissertation wurde am 22.11.2022 bei der Universität der Bundeswehr München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik (EIT) am 10.03.2023 angenommen. Die mündliche Prüfung fand am 12.04.2023 statt.

#### **Declaration**

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other university. This dissertation is my own work and contains nothing which is the outcome of work done in collaboration with others, except as specified in the text and Acknowledgements.

Prajith Kumar Poongodan April 2023

#### Acknowledgements

First, I would like to thank my advisor Prof. Linus Maurer for his guidance, support and valuable insights throughout my doctoral studies. I would also like to thank my second examiner Prof. Ralf Brederlow for his valuable time in reviewing my manuscript and providing feedback.

This work was done in close collaboration between Fraunhofer EMFT and Universität der Bundeswehr München. I would like to thank my group manager Frank Vanselow who initiated this project and trusted me with it for my doctoral work. I appreciate his support, guidance and mentorship to go deeper with my research work and his valuable technical insights. Special thanks to David Borggreve and Pragoti Bora who decided to accept me to work with them for my master thesis which brought me into the circuit design team. I had wonderful learning experience and fun during all our technical discussions. Furthermore, I would like to express my thanks to Enno Böhme for all the support during the tapeouts and help with the digital designs. Thanks to Oleg Sakolski whose master thesis contribution was very important to this work. I would also like to thank my other colleagues at the circuit design group Radu Ciocoveanu, Erkan Isa, Harshitha Basavaraju, Lei Zhang, Jakob Stuprich, Ferdinand Pscheidl, Pengcheng Xu, Sebastian Ruping, Aleksander Bajt, Himadri Shekhar Bhattacharyya and Piyush Kumar for their support and wonderful time in the office.

I would also like to thank the ProTaktilUS project consortium partners at Fraunhofer IPMS, Fraunhofer IKTS and Fraunhofer IFF for their assistance throughout the project and the wonderful working environment created during the project.

Finally, I would like to thank my parents Janardhanan and Preetha and my brother Hari for their continuous support over these years. I would like to express my deepest gratitude to my wife Vaani for being exceptionally understanding, supportive and encouraging throughout the years.

#### **Abstract**

Ultrasound based sensing modality is one of the oldest in medical and industrial applications. Advancements in micromachining techniques opened up possibilities to develop micromachined ultrasonic transducers (MUTs). Of these, capacitive micromachined ultrasonic transducer (CMUT) technology has proven to be a promising alternative to conventional bulk piezoelectric based ultrasonic transducers. This enabled the design and development of miniaturized CMUT based sensor solutions for a wide range of applications. The medical imaging has benefited a lot from the advancements in CMUT fabrication technology. Advances in high voltage (HV) integrated circuit design processes for high voltage and high power applications opened up the opportunity to design highly compact application specific integrated circuits (ASIC) for such transducers. The CMOS compatibility of CMUTs makes it a very attractive option for a monolithic integrated CMUT sensor system.

In this thesis, the design of integrated circuits to interface a CMUT array is addressed. Circuit architectures are investigated and implemented to enable a highly integrated CMUT-ASIC system. A novel CMUT driving architecture is presented which eliminates the need to use an external bias tee circuit to bias the CMUT to HV levels. The structure also helps to avoid the use of HV isolation switch in the receive path of the transceiver channel. This reduces the die area and helps to improve the signal to noise ratio (SNR). Design and implementation of an 8 channel transceiver ASIC in 0.18 µm HV silicon on insulator (SOI) technology is presented. Design of key circuit blocks in the transmit path including HV pulsers, level-shifters, HV linear regulator and other auxillary circuits are provided and the performance verification through silicon measurements are also presented. In the receive path, a resistive feedback transimpedance amplifier (TIA) is used for converting the timevarying input current into an output voltage. Four adjustable gain settings are possible for the designed TIA. Measurement results are provided which validates the analysis and design presented. A pulse-echo measurement result demonstrates the capability of the complete system to be operated as proposed.

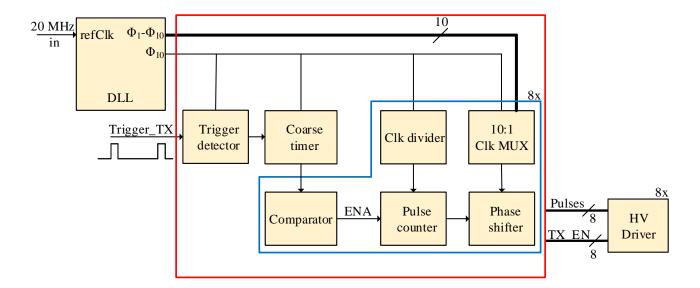

A transmit beamforming circuit for phased array actuation of CMUT arrays is presented in the final part of the thesis. An architecture combining an analog wide-range delay locked loop (DLL) and digital circuits is implemented. Such a very low-power area efficient approach demonstrates the possibilities of circuit integration on front-end ASICs for CMUT based imaging devices. Extensive simulation results presents the feasibility of the proposed solution to perform a high resolution beam focusing and steering using only a single low frequency clock source. The digital circuit blocks provide further flexibility to the ASIC by adding of frequency division and pulse count functionality.

#### Kurzfassung

Ultraschall ist eine der ältesten Sensormethoden für medizinische und industrielle Anwendungen. Fortschritte in der Mikrofertigungstechnik ermöglichen die Entwicklung mikromechanischer Ultraschallwandler (MUTs). Die Technologie der kapazitiven mikromechanischen Ultraschallwandler (CMUT) hat sich dabei als vielversprechende Alternative zu konventionellen Ultraschallwandlern auf piezoelektrischer Basis erwiesen. Dies ermöglichte das Design und die Entwicklung von miniaturisierten CMUT-basierten Sensorlösungen für ein breites Spektrum von Anwendungen. Die medizinische Bilderzeugung hat stark von den Fortschritten in der CMUT-Technologie profitiert. Fortschritte bei der Entwicklung integrierter Hochspannungsschaltungen für Hochspannungs- und Hochleistungsanwendungen ermöglichten die Entwicklung hochkompakter anwendungsspezifischer integrierter Schaltungen (ASIC) für solche Wandler. Die CMOS-Kompatibilität von CMUTs macht sie zu einer sehr attraktiven Option für ein monolithisch integriertes CMUT-Sensorsystem.

In dieser Doktorarbeit wird der Entwicklung integrierter Schaltungen für die Schnittstelle eines CMUT-Arrays behandelt. Es werden Schaltungsarchitekturen untersucht und implementiert, um ein hochintegriertes CMUT-ASIC-System zu ermöglichen. Es wird eine neuartige CMUT-Ansteuerungsarchitektur vorgestellt, die den externen Biaseinspeisungsschaltkreis zur Einstellung des CMUT auf HV Pegel vermeidet. Die Struktur trägt auch dazu bei, den Hochspannungsisolationsschalter im Empfangspfad des Transceiverkanals zu vermeiden. Dies reduziert die Chipfläche und trägt zur Verbesserung des Signal-Rausch-Verhältnisses (SNR) bei. Es wird der Entwurf und die Implementierung eines 8 Kanal Transceiver ASICs in Silizium-auf-Isolator (SOI) Technologie vorgestellt. Das Design der wichtigsten Schaltungsblöcke im Sendepfad, einschließlich HV Pulsern, Pegelumsetzern, Hochspannungslinearreglern und anderen Zusatzschaltungen, wird vorgestellt und die Leistungsüberprüfung durch Siliziummessungen wird ebenfalls präsentiert. Im Empfangsweg wird ein Transimpedanzverstärker (TIA) mit Widerstandsrückkopplung zur Umwandlung des zeitvariablen Eingangsstroms in eine Ausgangsspannung verwendet. Für den entwickelten TIA sind vier einstellbare Verstärkungseinstellungen möglich. Es werden Messergebnisse vorgelegt, die die vorgestellte Analyse und den Entwurf validieren. Die Ergebnisse einer

Puls-Echo Messung zeigen, das der entwickelte Prototyp in der Applikation wie gewünscht funktioniert.

Im letzten Teil der Doktorarbeit wird eine Transmit Beamforming Schaltung für phasengesteuerten Arraybetrieb von CMUT-Arrays vorgestellt. Es wird eine Architektur implementiert, die eine analoge Delay Locked Loop (DLL) mit hoher Bandbreite und digitale Schaltungen kombiniert. Dieser sehr stromsparende und flächeneffiziente Ansatz demonstriert die Möglichkeiten der Schaltungsintegration auf Front-End-ASICs für CMUT-basierte Bildgebungsgeräte. Ausführliche Simulationsergebnisse zeigen die Realisierbarkeit der vorgeschlagenen Lösung für eine hochauflösende Strahlfokussierung und -steuerung mit nur einer einzigen niederfrequenten Taktquelle. Die digitalen Schaltungsblöcke bieten weitere Flexibilität für den ASIC durch zusätzliche Funktionen zur Frequenzteilung und Impulszählung.

## **Table of contents**

| Li | st of f  | igures                                                                | xiii |

|----|----------|-----------------------------------------------------------------------|------|

| Li | st of t  | ables                                                                 | xix  |

| Li | st of A  | Acronyms                                                              | xxi  |

| Li | st of S  | Symbols                                                               | XXV  |

| 1  | oduction | 1                                                                     |      |

|    | 1.1      | Motivation and research objective                                     | 2    |

| 2  | Ultr     | asound System                                                         | 7    |

|    | 2.1      | Conventional CMUT driving architecture                                | 7    |

|    | 2.2      | Proposed CMUT driving architecture                                    | 8    |

|    | 2.3      | Ultrasonic Transceiver Chip Architecture                              | 10   |

|    | 2.4      | High Voltage Process Technology                                       | 14   |

| 3  | Inte     | grated Circuits for CMUT Transceiver Interface                        | 17   |

|    | 3.1      | Background                                                            | 17   |

|    | 3.2      | High Voltage Transmit Pulser Circuit                                  | 18   |

|    |          | 3.2.1 Static level shifter based pulser design                        | 19   |

|    |          | 3.2.2 Gate charge recycled level shifter based pulser                 | 23   |

|    |          | 3.2.3 Nanosecond delay dynamic level shifter based pulser circuit     | 26   |

|    | 3.3      | High Voltage, Fast Transient Response and High Current Sinking Linear |      |

|    |          | Regulator                                                             | 34   |

|    |          | 3.3.1 Measurement results                                             | 43   |

|    | 3.4      | Low Voltage Receiver Front-End Design                                 | 46   |

|    |          | 3.4.1 Open-loop transimpedance amplifiers                             | 46   |

|    |          | 3.4.2 Feedback transimpedance amplifiers                              | 18   |

**xii** Table of contents

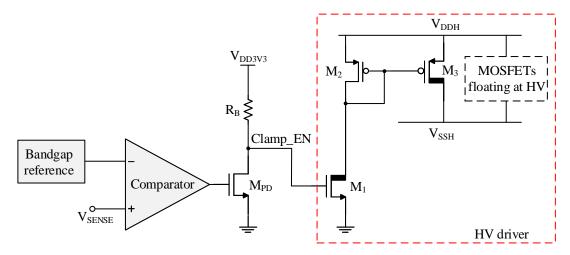

|    | 3.5            | Start-ı  | ıp clamp circuit                                           | 65  |

|----|----------------|----------|------------------------------------------------------------|-----|

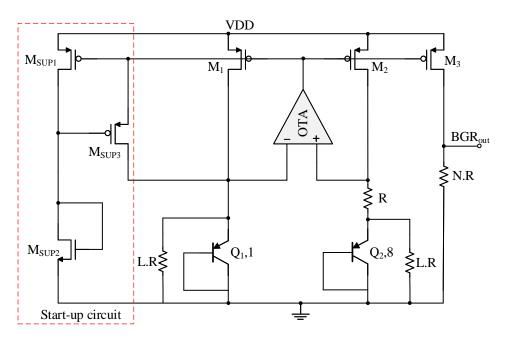

|    |                | 3.5.1    | Bandgap reference circuit                                  | 66  |

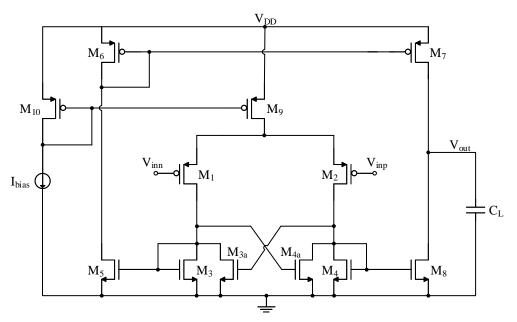

|    |                | 3.5.2    | Symmetric OTA                                              |     |

|    | 3.6            | Transc   | ceiver Chip Performance and Comparison to State of the Art | 69  |

| 4  | Trai           | nsmit B  | eamforming Circuit Design                                  | 75  |

|    | 4.1            | Introd   | uction                                                     | 75  |

|    | 4.2            | Beam     | forming architectures                                      | 76  |

|    | 4.3            | Delay    | Locked Loop                                                | 79  |

|    |                | 4.3.1    | Frequency response                                         | 80  |

|    |                | 4.3.2    | DLL operation                                              | 81  |

|    |                | 4.3.3    | Voltage controlled delay line design                       | 87  |

|    |                | 4.3.4    | Dynamic phase detector                                     | 91  |

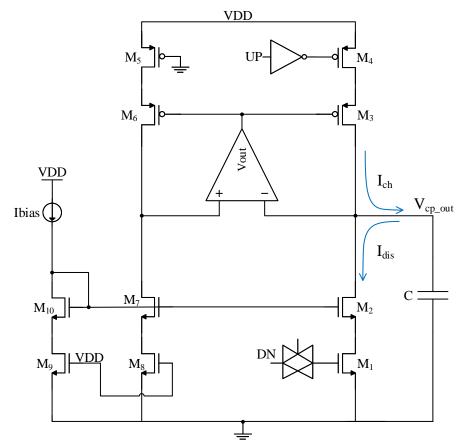

|    |                | 4.3.5    | Charge pump                                                | 94  |

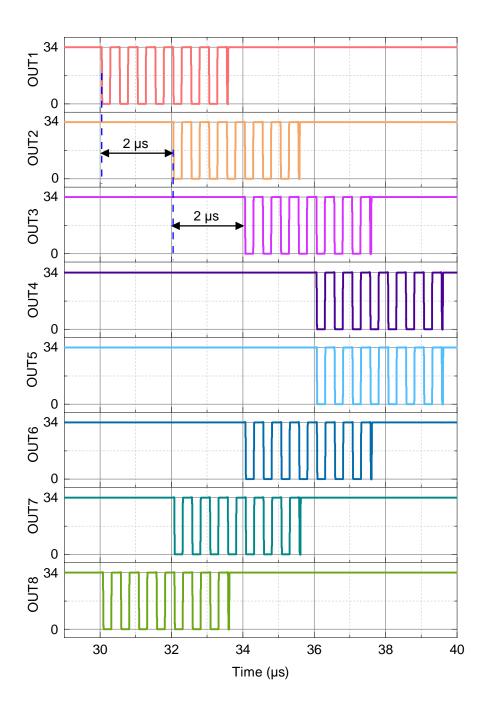

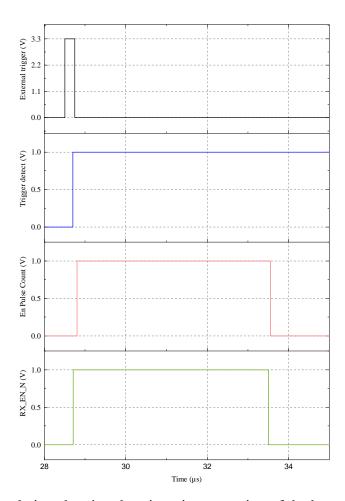

|    |                | 4.3.6    | Transmit beamforming output simulation results             | 109 |

| 5  | Con            | clusion  |                                                            | 113 |

|    | 5.1            | Summ     | nary                                                       | 113 |

|    | 5.2            | Enhan    | cement to state of the art                                 | 115 |

| Re | eferen         | ices     |                                                            | 117 |

| Li | st of <b>j</b> | publicat | tions                                                      | 125 |

| Ar | opend          | lix A V  | Verilog codes                                              | 127 |

# List of figures

| 1.1 | Cross section view of a conventionally used bulk piezoelectric transducer                           | 2  |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 1.2 | Cross section view of a Capacitive Micromachined Ultrasonic Transducer                              |    |

|     | (CMUT)                                                                                              | 4  |

| 1.3 | (a) Circuit used to interface the CMUT when operated as an ultrasound                               |    |

|     | transmitter; (b) Circuit interface for the CMUT when used as an ultrasound                          |    |

|     | receiver                                                                                            | 5  |

| 2.1 | A conventional block diagram of ultrasound based system                                             | 7  |

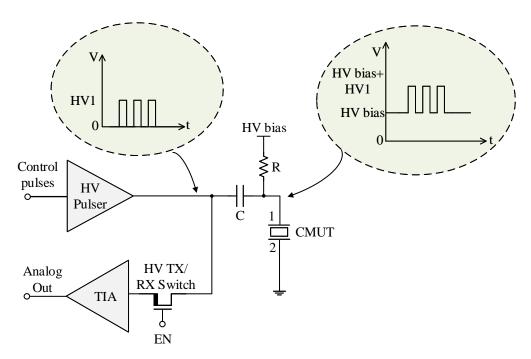

| 2.2 | A conventionally used driving structure for a pulse-echo operation                                  | 9  |

| 2.3 | The proposed transmit-receive structure for the pulse-echo operation                                | 10 |

| 2.4 | Block diagram representation of the designed CMUT transceiver ASIC                                  | 11 |

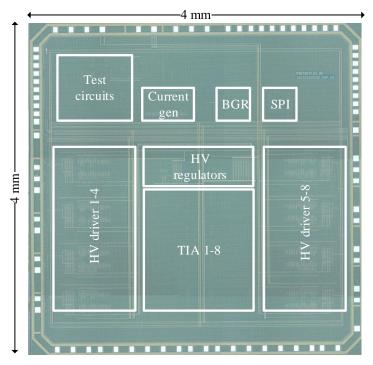

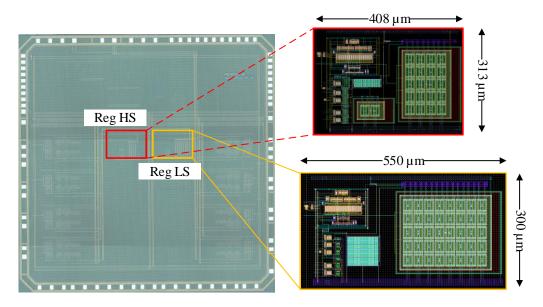

| 2.5 | Microphotograph of the ProTaktilUS_A0 chip                                                          | 12 |

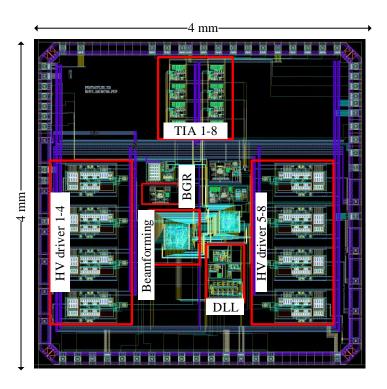

| 2.6 | Microphotograph of the ProTaktilUS_B0 chip                                                          | 12 |

| 2.7 | Chip layout of the ProTaktilUS_C0 chip which is under fabrication                                   | 13 |

| 2.8 | Cross section view of a super junction high voltage NMOS (LNDMOS)                                   |    |

|     | transistor [14], [15]                                                                               | 14 |

| 2.9 | Symbols used for the different MOSFETs used in designs                                              | 15 |

| 3.1 | The top-level block diagram of the high voltage pulser circuit                                      | 18 |

| 3.2 | Static level shifter based pulser circuit                                                           | 19 |

| 3.3 | Current limited static level shifter based pulser circuit                                           | 20 |

| 3.4 | High voltage output of the pulser circuit                                                           | 21 |

| 3.5 | Gate drive signals of the push-pull stage                                                           | 21 |

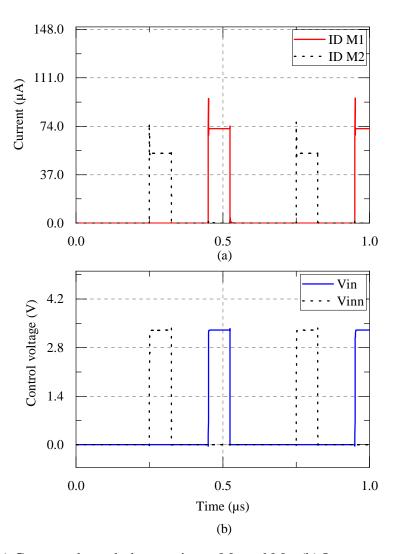

| 3.6 | Current through transistors $M_1$ and $M_2$                                                         | 22 |

| 3.7 | Gate charge recycled level shifter based pulser circuit                                             | 23 |

| 3.8 | (a) Simulation results showing gate drive signal of the low-side and high-side;                     |    |

|     | (b) Output of the pulser circuit                                                                    | 24 |

| 3.9 | (a) Currents through the transistors M <sub>1</sub> and M <sub>2</sub> : (b) Input control signals. | 25 |

**xiv** List of figures

| 3.10 | Dynamic level shifter based pulser circuit                                    | 26 |

|------|-------------------------------------------------------------------------------|----|

| 3.11 | (a) Post-layout simulation showing the HV pulser output and the high side     |    |

|      | and low side gate drive voltages of the push-pull stage; (b) Simulation       |    |

|      | showing the drain currents through the transistors $M_1$ and $M_2$            | 28 |

| 3.12 | Die photo and layout of the pulser circuit highlighted                        | 29 |

| 3.13 | The test PCB with the two transceiver chips and external control and power    |    |

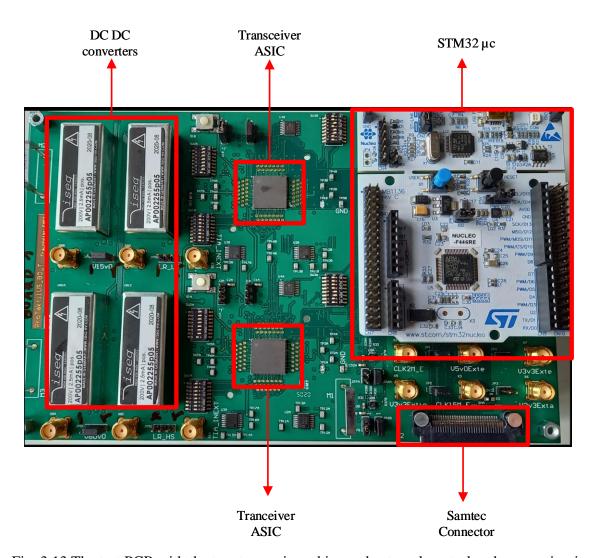

|      | circuits                                                                      | 31 |

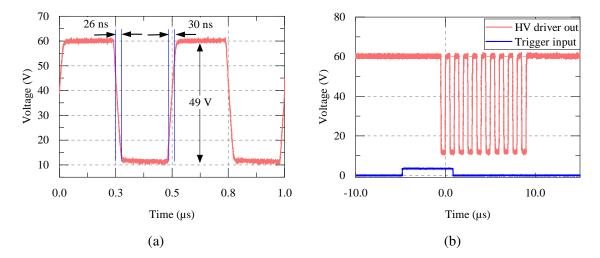

| 3.14 | (a) Measured output of the HV pulser circuit at 2 MHz; (b) pulser output      |    |

|      | showing response to an input triggering signal                                | 32 |

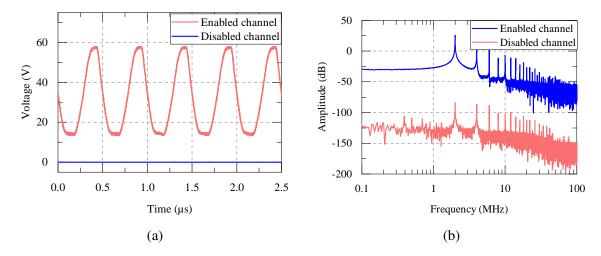

| 3.15 | (a) Measured crosstalk between two adjacent HV pulser channels; (b) Fre-      |    |

|      | quency spectrum of the two channels                                           | 32 |

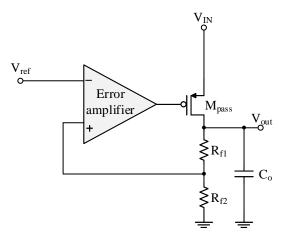

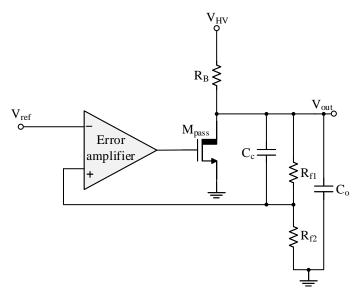

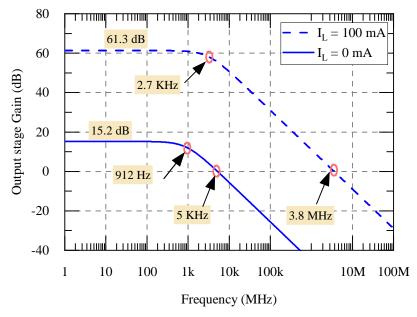

| 3.16 | A PMOS pass transistor LDO                                                    | 34 |

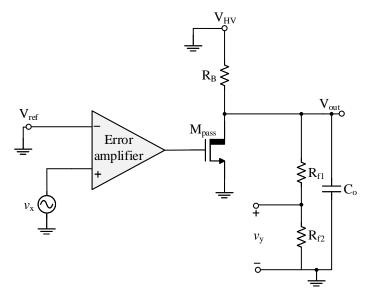

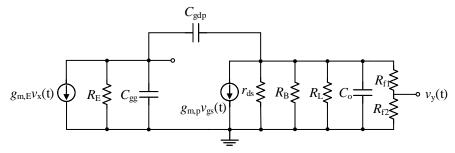

| 3.17 | The designed HV linear regulator topology with current sinking capability     | 35 |

| 3.18 | Small-signal gain presented by the output stage for maximum and minimum       |    |

|      | load conditions                                                               | 36 |

| 3.19 | AC circuit of the linear regulator used to derive the small-signal equivalent |    |

|      | circuit                                                                       | 37 |

| 3.20 | Small-signal equivalent circuit of the HV regulator. The compensation         |    |

|      | capacitor is not shown.                                                       | 37 |

| 3.21 | Small-signal equivalent circuit of the HV regulator with lead compensation    |    |

|      | capacitor connected                                                           | 38 |

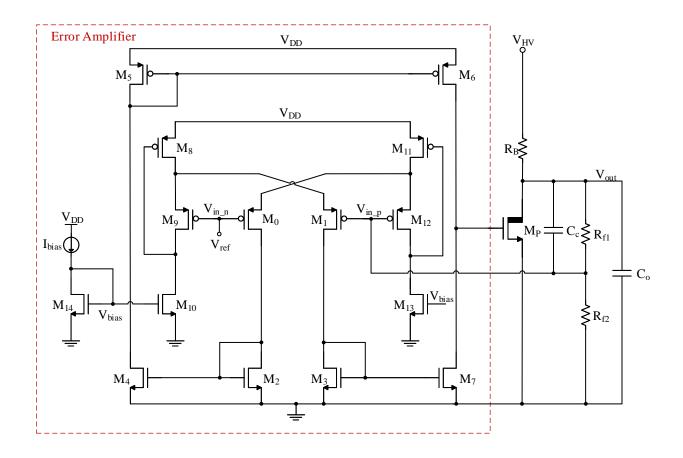

|      | Schematic of the linear regulator with a class AB error amplifier             | 40 |

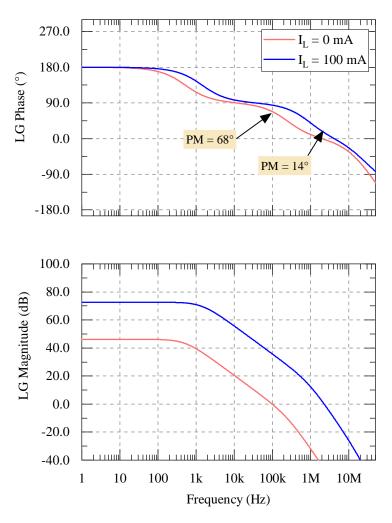

| 3.23 | Magnitude and phase response plot of the loop-gain of the uncompensated       |    |

|      | regulator at the two dc operating points                                      | 41 |

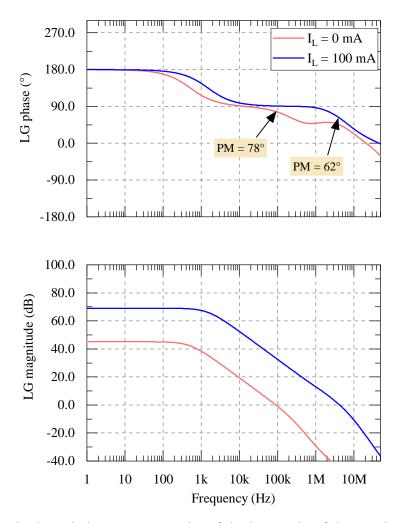

| 3.24 | Magnitude and phase response plot of the loop-gain of the regulator at the    |    |

|      | two dc operating points after adding the compensation capacitor               | 42 |

|      | Die photo and layout of the HV linear regulators highlighted                  | 43 |

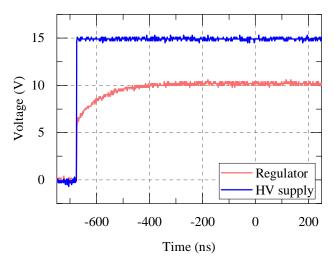

| 3.26 | Measurement results showing the start up behavior of the low side HV          |    |

|      | regulator. The regulator settles to around 10.2 V in 270 ns                   | 43 |

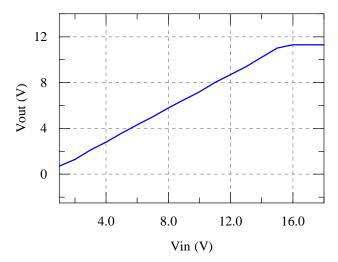

| 3.27 | Measurement result showing the line regulation behavior of the low-side       |    |

|      | regulator                                                                     | 44 |

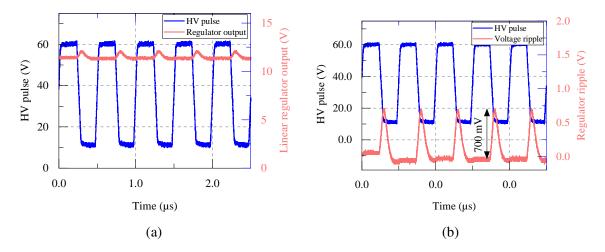

| 3.28 | (a) Measurement result showing the transient load response of the 11 V        |    |

|      | linear regulator when all 8 channels of the HV pulsers are turned on; (b) The |    |

|      | regulator output ripple voltage after AC coupling the output voltage          | 44 |

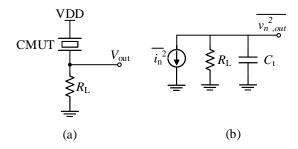

|      | (a) Conversion of CMUT current to voltage output; (b) Equivalent circuit.     | 46 |

| 3.30 | (a) Schematic of the CG-TIA; (b) Regulated cascode CG-TIA                     | 47 |

List of figures xv

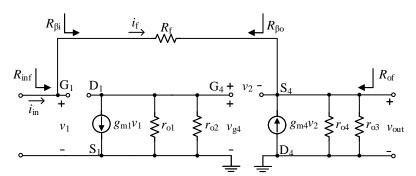

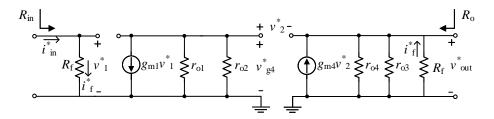

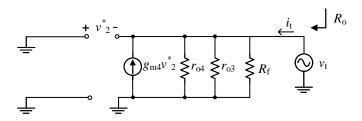

| 3.31  | (a) A feedback TIA with common gate input stage (Shunt-shunt feedback          |    |

|-------|--------------------------------------------------------------------------------|----|

|       | amplifier); (b) Closed loop small-signal model                                 | 48 |

| 3.32  | Open loop small-signal model of Fig. 3.31b                                     | 49 |

| 3.33  | Schematic diagram of a resistive feedback transimpedance amplifier             | 50 |

| 3.34  | Closed-loop small signal model of the TIA                                      | 50 |

| 3.35  | Open-loop small signal model of the TIA                                        | 51 |

| 3.36  | Open loop small-signal model to calculate the output resitance of the TIA      | 51 |

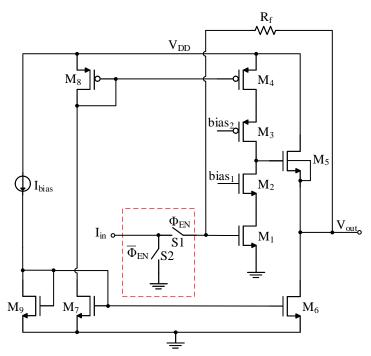

| 3.37  | Schematic diagram of the designed resistive feedback transimpedance amplifier. | 53 |

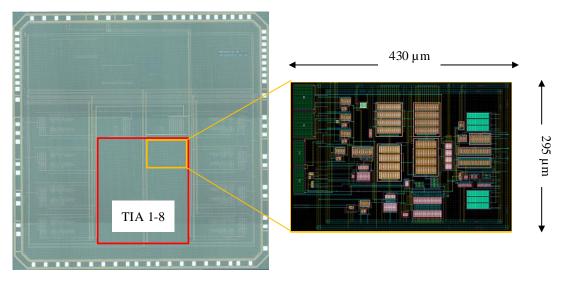

| 3.38  | Die photo and the layout of the receiver circuit is highlighted                | 54 |

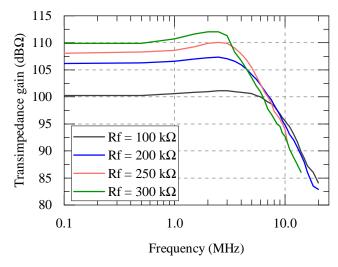

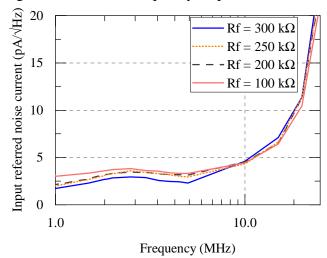

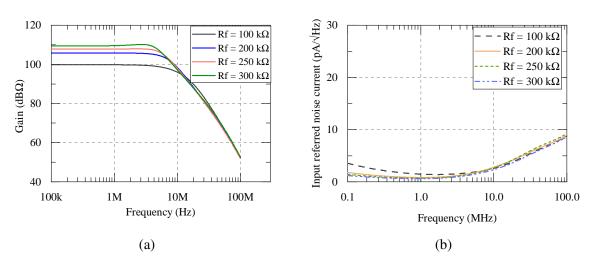

| 3.39  | Measured frequency response of the TIA                                         | 55 |

| 3.40  | Measured input-referred noise current                                          | 55 |

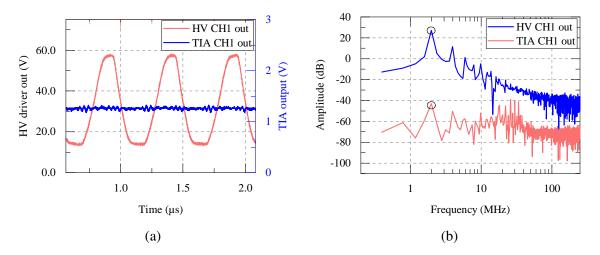

| 3.41  | (a) Measured crosstalk between one HV pulser channel and the TIA of the        |    |

|       | same channel; (b) Frequency spectrum of the two circuits                       | 56 |

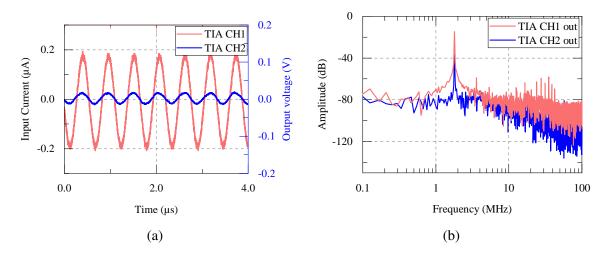

| 3.42  | (a) Measured crosstalk between two adjacent receive channels; (b) Frequency    |    |

|       | spectrum of the two channels.                                                  | 57 |

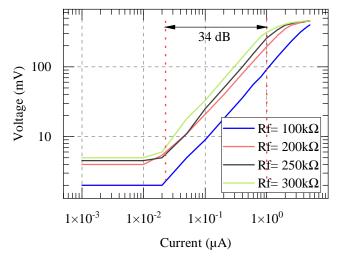

| 3.43  | Measurement data showing the TIA dynamic range                                 | 57 |

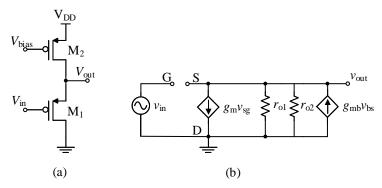

| 3.44  | (a) A PMOS source follower; (b) small-signal equivalent circuit                | 58 |

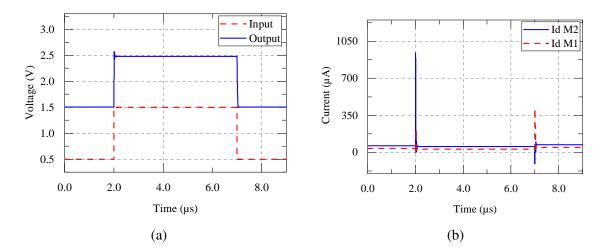

| 3.45  | Schematic diagram of a super source voltage follower                           | 59 |

| 3.46  | Small-signal equivalent circuit of the super source voltage follower           | 60 |

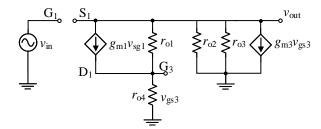

| 3.47  | (a) Simulated response of the SSF to a step input voltage; (b) Drain currents  |    |

|       | of the transistors $M_2$ and $M_1$                                             | 62 |

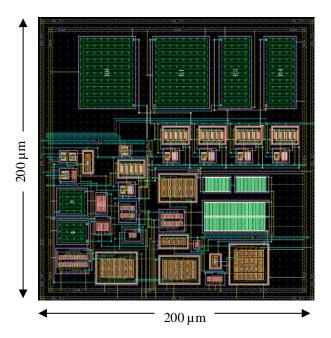

| 3.48  | Layout of the TIA with super source follower                                   | 63 |

| 3.49  | (a) Gain of the receiver; (b) Input referred noise of the receiver             | 64 |

| 3.50  | Block diagram of the start-up monitor circuit                                  | 65 |

| 3.51  | Schematic of the 1 V bandgap voltage reference circuit                         | 66 |

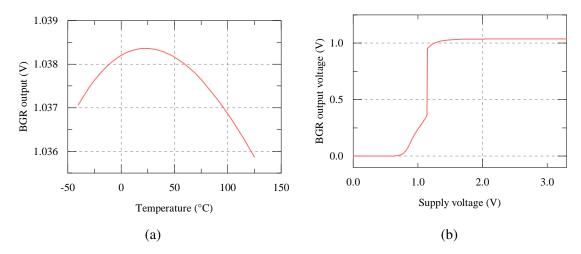

| 3.52  | (a)Post-layout simulation showing the BGR output voltage against tempera-      |    |

|       | ture sweep; (b) BGR output variation with a dc sweep of the supply voltage.    | 67 |

| 3.53  | Schematic of the OTA used as comparator                                        | 68 |

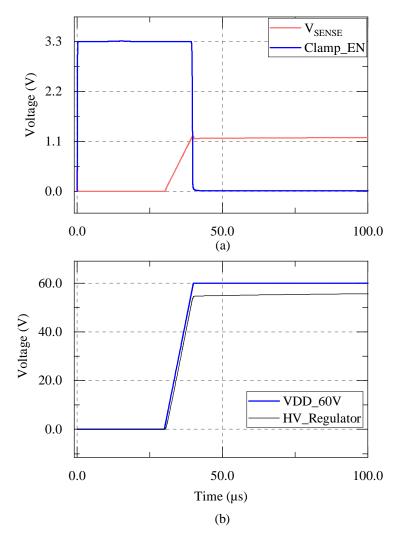

| 3.54  | (a) Plot showing the operation of the clamp circuit; (b) the 60 V power supply |    |

|       | ramp-up and the ramp-up of the $56\ V$ linear regulator is also shown here     | 69 |

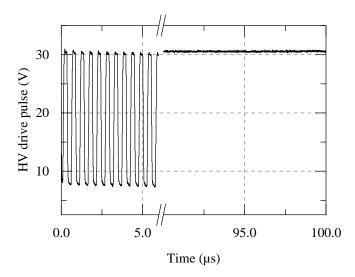

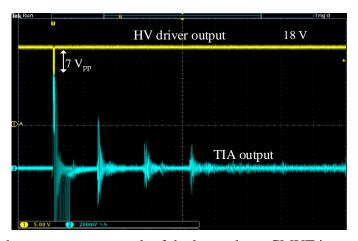

| 3.55  | High voltage pulses applied to the airborne CMUT under test                    | 72 |

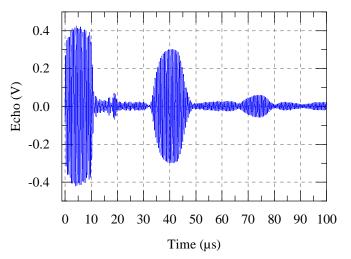

| 3.56  | Echo received at the output of the transimpedance amplifier measured by        |    |

|       | oscilloscope with the target at approximately 1 cm from the CMUT               | 73 |

| 3.57  | Pulse-echo measurement result of the low voltage CMUT immersed in              |    |

|       | silicone oil                                                                   | 74 |

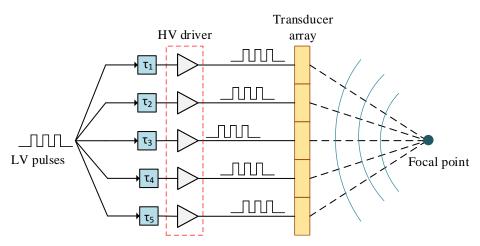

| 4.1   | Illustration of the transmit beamforming using a CMUT array                    | 76 |

| -T. I | musuation of the transmit beamforming using a Civio I allay                    | 70 |

xvi List of figures

| 4.2  | Block diagram of the digital beamforming architecture presented in                | 77  |

|------|-----------------------------------------------------------------------------------|-----|

| 4.3  | Block diagram of the proposed DLL based transmit beamformer circuit               | 78  |

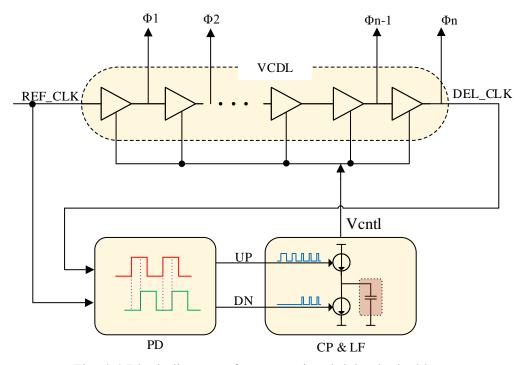

| 4.4  | Block diagram of a conventional delay locked loop                                 | 79  |

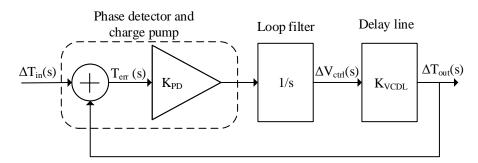

| 4.5  | S-domain linear model of the DLL                                                  | 80  |

| 4.6  | Illustration of DLL locking operation and frequency locking range                 | 82  |

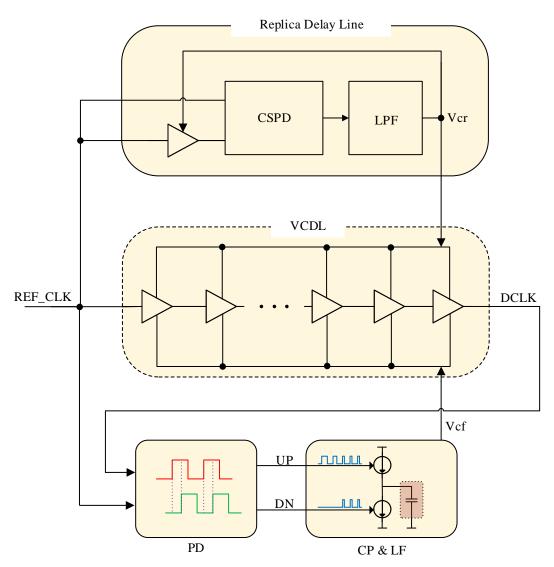

| 4.7  | A wide range DLL with a replica delay line (RDL)                                  | 84  |

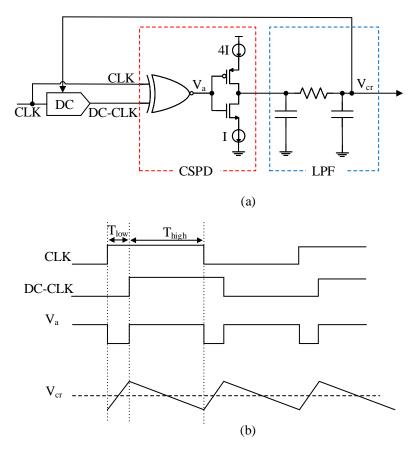

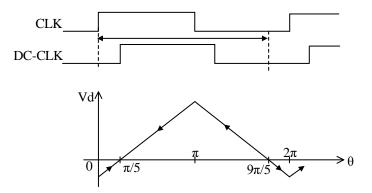

| 4.8  | Replica delay line with current steering phase detector (CSPD) and represen-      |     |

|      | tation of waveforms showing operation                                             | 85  |

| 4.9  | Gain curve of the CSPD and locking range                                          | 86  |

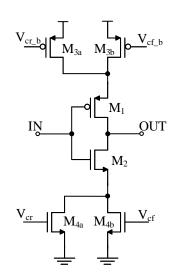

| 4.10 | Schematic diagram of a current starved delay cell with dual control               | 87  |

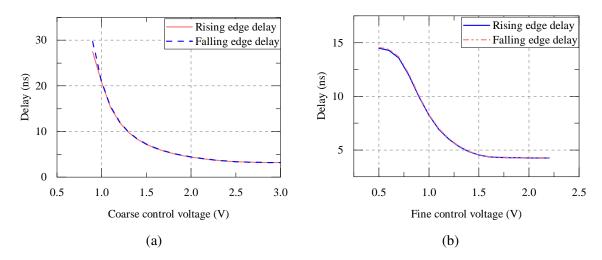

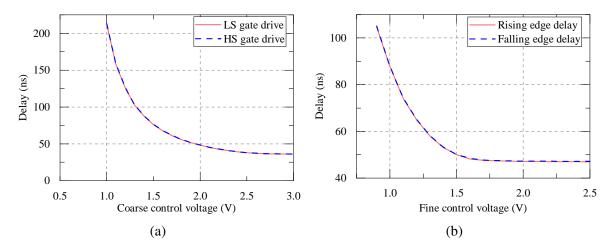

| 4.11 | (a) Post-layout simulation result showing the delay variation against a sweep     |     |

|      | of coarse control voltage. The fine control voltage set at 800 mV; (b) delay      |     |

|      | variation against sweep of fine control voltage. Coarse control voltage set at    |     |

|      | 1.2 V                                                                             | 88  |

| 4.12 | (a) Post-layout simulation result showing the delay variation of the complete     |     |

|      | delay line against a sweep of coarse control voltage. The fine control voltage    |     |

|      | set at 800 mV; (b) delay variation of delay line against sweep of fine control    |     |

|      | voltage. Coarse control voltage set at 1.2 V                                      | 89  |

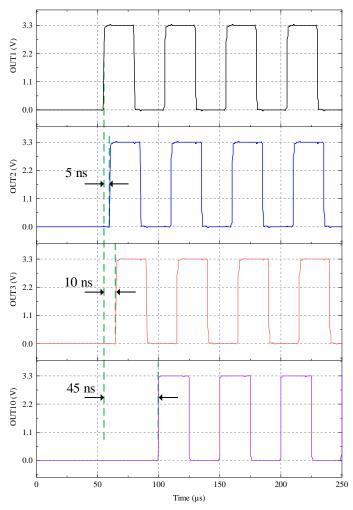

| 4.13 | Transient simulation of the delay line with a 20 MHz clock input. The coarse      |     |

|      | control voltage is set at 2 V and fine control voltage at 800 mV $ \dots  \dots $ | 90  |

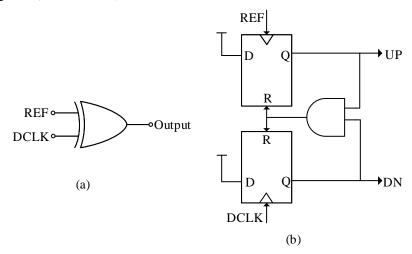

| 4.14 | (a) An XOR phase detector, (b) a phase-frequency detector                         | 91  |

| 4.15 | Schematic diagram of the dynamic phase detector circuit to generate the UP        |     |

|      | and DN control signals for the charge pump                                        | 92  |

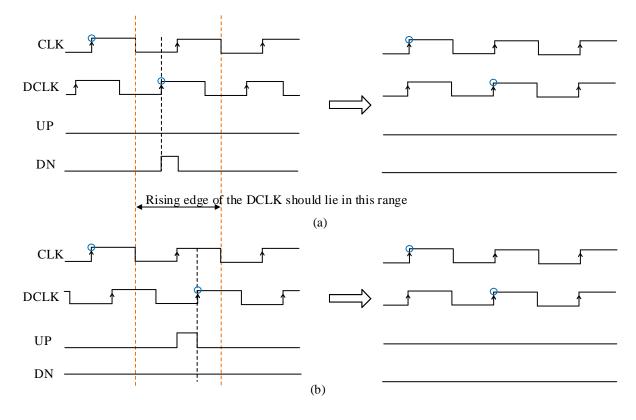

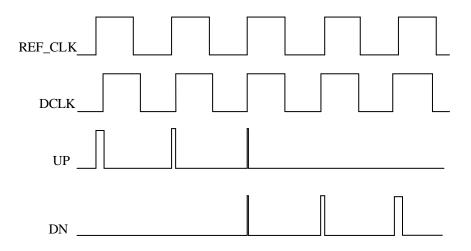

| 4.16 | Waveforms showing the operation of the PD                                         | 92  |

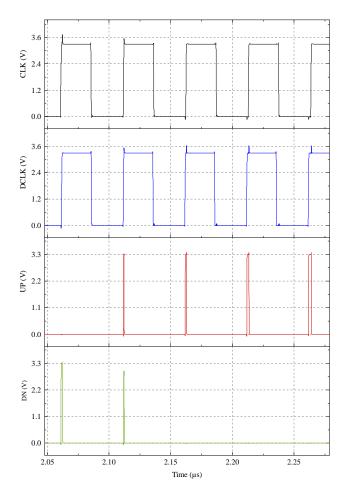

| 4.17 | Simulation result showing the operation of the dynamic phase detector             | 93  |

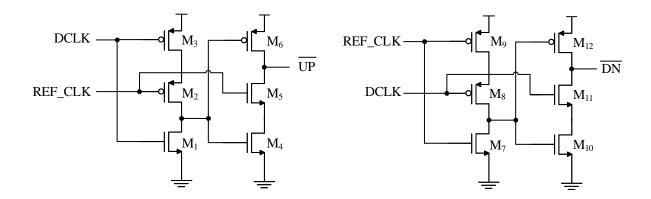

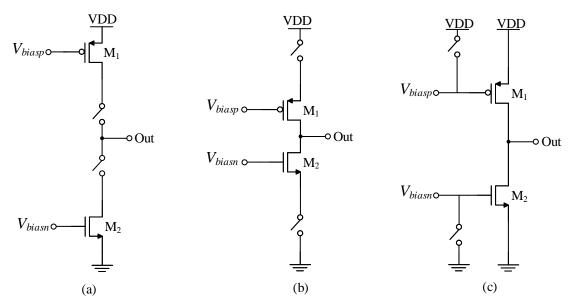

| 4.18 | (a) Drain-switched charge pump, (b) source-switched charge pump, (c) gate-        |     |

|      | switched charge pump                                                              | 94  |

| 4.19 | A conventional source-switched charge pump and its charge and discharge           |     |

|      | operation                                                                         | 95  |

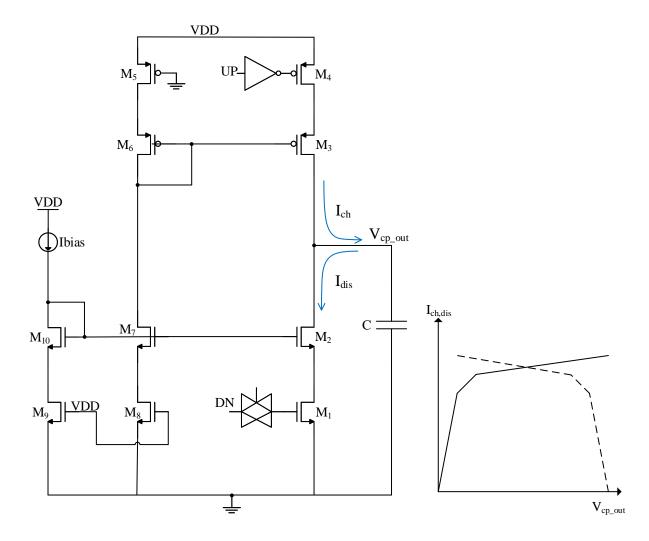

| 4.20 | Designed charge pump and loop filter                                              | 97  |

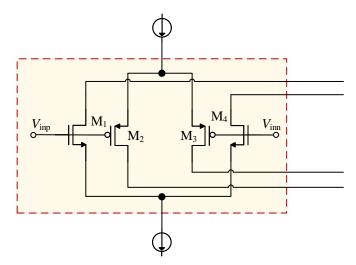

| 4.21 | Complementary input stage for rail to rail input operation                        | 98  |

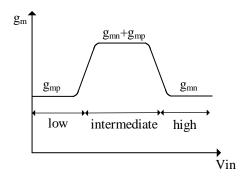

| 4.22 | Transconductance $g_{mtot}$ of the complementary input stage versus the common-   |     |

|      | mode input voltage                                                                | 99  |

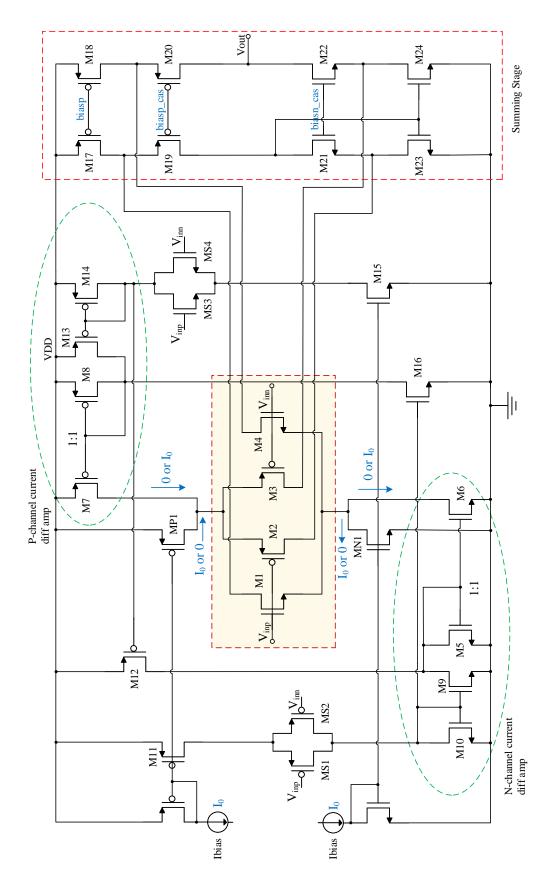

| 4.23 | Schematic diagram of the complete rail to rail input OTA                          | 100 |

| 4.24 | Post-layout simulation showing the frequency response of the rail to rail         |     |

|      | input OTA                                                                         | 101 |

List of figures xvii

| 4.25 | Frequency response of the rail to rail amplifier showing the results at the             |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | nominal corner and the worst identified corner                                          | 102 |

| 4.26 | Post-layout simulation showing the variation of $g_{\text{mtot}}$ versus the input com- |     |

|      | mon mode voltage                                                                        | 103 |

| 4.27 | Post-layout simulation showing the variation of DC open-loop gain versus                |     |

|      | the input common mode voltage                                                           | 104 |

| 4.28 | Layout of the charge pump and loop filter with rail to rail OTA and biasing             |     |

|      | circuits                                                                                | 104 |

| 4.29 | Post-layout dc simulation showing the variation of the charging and discharg-           |     |

|      | ing currents of the charge pump versus the control voltage variation at the             |     |

|      | loop filter output                                                                      | 105 |

| 4.30 | Layout of the complete multi-phase clock generator DLL                                  | 105 |

| 4.31 | Post-layout simulation results showing the transient response of the reference          |     |

|      | clock and delayed clock; (a) transient simulation showing the misaligned                |     |

|      | reference clock and the feedback clock (output from tap 10) after start up;             |     |

|      | (b) fully aligned clocks after DLL achieved locked state                                | 106 |

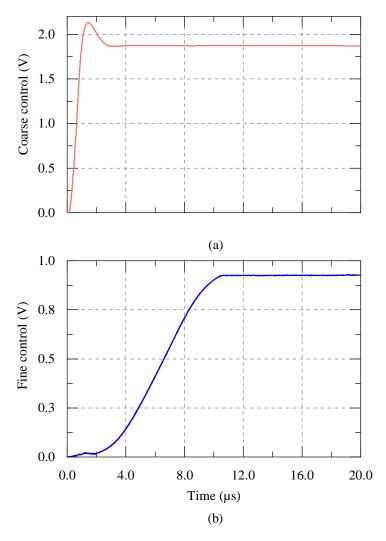

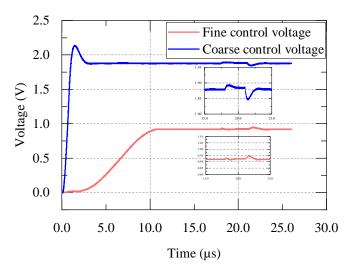

| 4.32 | Transient simulation showing the coarse and fine control voltages of the DLL.           | 107 |

| 4.33 | Post-layout transient simulation showing the control voltage response for a             |     |

|      | frequency jump in the reference clock                                                   | 108 |

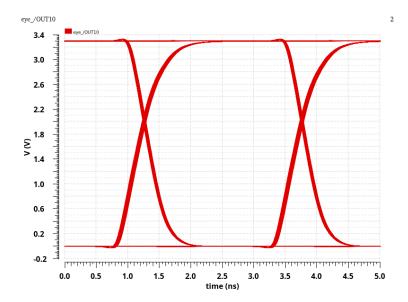

| 4.34 | Eye diagram of the DLL                                                                  | 108 |

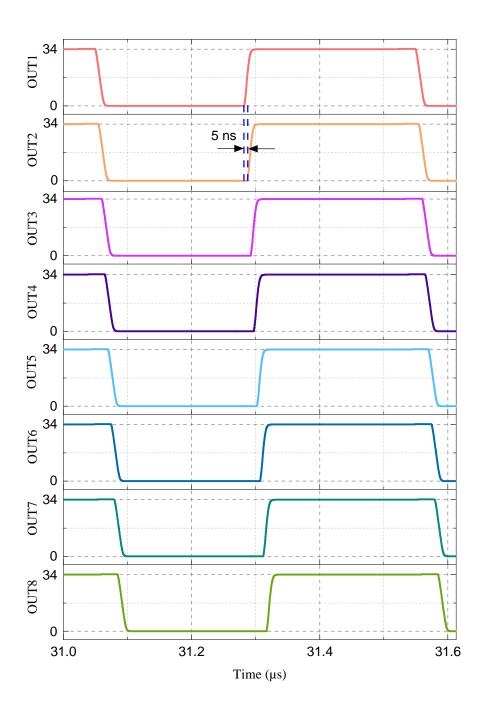

| 4.35 | Transient simulation showing the output of the HV driver after applying the             |     |

|      | delays. Each HV driver channel is separated by the DLL delay of 5 ns                    | 110 |

| 4.36 | Transient simulation showing the output of the HV driver after applying the             |     |

|      |                                                                                         | 111 |

| 4.37 | Simulation showing the triggering operation of the beamforming block                    | 112 |

## List of tables

| 3.1  | 6 bit clock division                                                              | 30  |

|------|-----------------------------------------------------------------------------------|-----|

| 3.2  | Measured performance parameter of the HV pulser circuit compared with             |     |

|      | prior art                                                                         | 33  |

| 3.3  | Performance parameters of the low side linear regulator                           | 45  |

| 3.4  | Dynamic range of the TIA for different gain setting                               | 56  |

| 3.5  | Performance parameters of the super source follower                               | 62  |

| 3.6  | Measured performance parameter of the TIA circuit compared with prior art         | 64  |

| 3.7  | Design values for the BGR circuit                                                 | 67  |

| 3.8  | System level comparison with state of the art                                     | 71  |

| 3.9  | Parameters of the CMUT used for testing                                           | 72  |

| 3.10 | Parameters of the CMUT used for fluid testing                                     | 74  |

| 11   | Design and all parties of an the unit to unit amplifies and the above ground land | 97  |

| 4.1  | Design specifications for the rail to rail amplifier and the charge pump loop     | 9/  |

| 4.2  | Performance parameters of the DLL                                                 | 108 |

## **List of Acronyms**

**ac** Alternating Current

**ASIC** Application Specific Integrated Circuit

**BCD** Bipolar CMOS DMOS

**BGR** Bandgap Reference

**BIST** Built in Self Test

**BOX** Buried Oxide

**BW** Bandwidth

**CBF** Current Boosting Factor

**CDR** Clock and Data Recovery

**CG** Common Gate

**CMRR** Common Mode Rejection Ratio

**CMUT** Capacitive Micromachined Ultrasonic Transducer

**CP** Charge Pump

**CS** Common Source

**CSPD** Current Steering Phase Detector

**CTAT** Complementary to Absolute Temperature

dc Direct Current

**DC** Delay Cell

**xxii** List of Acronyms

**DLL** Delay Locked Loop

**DTI** Deep Trench Isolation

**FFT** Fast Fourier Transform

**FOM** Figure of Merit

**FPGA** Field Programmable Gate Array

**GBW** Gain Bandwidth

**HIFU** High Intensity Focused Ultrasound

**HS** High Side

**HV** High Voltage

**HW** Handle Wafer

IC Integrated Circuit

ICE Intra-cardiac Echocardiography

**ICMR** Input Common-mode Range

**IVUS** Intra-vascular Ultrasound

**KCL** Kirchhoff's Current Law

**LDO** Low-dropout Linear Regulator

**LF** Loop Filter

**LNA** Low Noise Amplifier

**LPF** Low Pass Filter

LS Low Side

LV Low Voltage

**MEMS** Micro-electromechanical Systems

MOSFET Metal Oxide Semicondcutor Field Effect Transistor

**MUT** Micromachined Ultrasonic Transducers

MUX Multiplexer

**NDE** Non-destructive Evaluation

NMOS n-channel MOSFET

OTA Operational Transconductance Amplifier

**PCB** Printed Circuit Board

**PD** Phase Detector

**PFD** Phase Frequency Detector

PLL Phase Locked Loop

**PMOS** p-channel MOSFET

**PSS** Periodic Steady State

**PTAT** Proportional to Absolute Temperature

**PZT** Lead Zirconate Titanate

**RDL** Replica Delay Line

**RGC** Regulated Gate Cascode

**RX** Receive

**SPI** Serial Peripheral Interface

**SR** Slew Rate

**SSF** Super Source Follower

**SOI** Silicon on Insulator

**SONAR** Sound Navigation and Ranging

**TGC** Time Gain Compensation

**TIA** Transimpedance Amplifier

**TX** Transmit

**QFG** Quasi Floating Gate

xxiv List of Acronyms

**QFN** Quad Flat No Leads

**VCDL** Voltage Controlled Delay Line

VCO Voltage Controlled Oscillator

**VDE** Variable Delay Element

## **List of Symbols**

$\beta$  Feedback factor

$\mu_n$  Mobility of electrons

$\mu_p$  Mobility of holes

$\Omega$  Unit of resistance

$\tau$  Time constant of a circuit

$C'_{ox}$  Oxide capacitance per unit area of a MOSFET

$f_{-3dB}$  -3 dB bandwidth

$g_m$  Transconductance of a MOSFET

$g_{mb}$  Body transconductance of a MOSFET

*k* Boltzmann constant

r<sub>o</sub> Small-signal output resistance of a MOSFET

$V_{\rm bias}$  DC bias voltage on the CMUT

V<sub>BSmax</sub> Maximum bulk-source voltage of a MOSFET

$V_{\rm DSmax}$  Maximum drain-source voltage of a MOSFET

$V_{\text{GSmax}}$  Maximum gate-source voltage of a MOSFET

$V_{\rm pp}$  Peak to peak voltage

$V_{\rm th}$  Threshold voltage of the MOSFET

$\varepsilon$  Dielectric constant

xxvi List of Symbols

*ω* Angular frequency

$\phi$  Phase of the input signal

A Ampere

F Farad

dB Decibel

kHz Kilohertz

MHz Megahertz

## Chapter 1

## Introduction

Ultrasound refers to signals whose frequency range are above the audible range of 20 kHz. Ultrasound based imaging systems have been widely used for medical, industrial, automotive and consumer applications for decades. Ultrasound is also used by animals in the nature. A very well known example is that of bats. Bats emit ultrasound signals and when these signals strike an obstacle and bounce back, the bats use this information to locate the obstacle. Certain marine animals like Killer whale and dolphins use ultrasound for orientation and find their prey. This process is called echolocation or bio sonar. SONAR ( Sound Navigation and Ranging) was the first reported use of sound by humans. In 1826, Jean- Daniel Colladon, used an under water bell to measure the speed of sound in water in Lake of Geneva [1]. Based on this research, Colladon established a method to communicate between ships using acoustic signals and measure depth of sea using echo.

The discovery of piezoelectric effect pushed forward the practical use of ultrasound in medical and industry. The most commonly used applications for ultrasound are in the areas of medical imaging, non-destructive evaluation (NDE) in industry, automotive parking sensors, fluid flow measurements, robotics and high frequency ultrasonic probes for diagnosis and therapy. Based on applications, the frequency of the ultrasound can vary from a few kHz to few tens of MHz. Generally, for air based applications like range finding or distance measurement, few hundreds of kHz are used and for applications that require high resolution, ultrasound in MHz range is used. Some of the applications which require ultrasound in MHz range are high intensity focused ultrasound (HIFU), catheter based applications such as Intravascular ultrasound imaging (IVUS) and Intra-cardiac echocardiography (ICE) and doppler ultrasound.

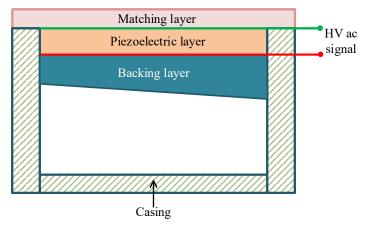

Conventionally, a piezo ceramic based transducer is used to generate the ultrasonic waves. A cross-section view of such a piezoelectric transducer is shown in Fig. 1.1. A piezoelectric material layer (usually lead zirconate titanate (PZT)) is placed between two electrodes. The

2 Introduction

Fig. 1.1 Cross section view of a conventionally used bulk piezoelectric transducer.

resonant frequency of the transducer depends directly on the thickness of this layer. Precise deposition of a thin piezoelectric layer is required for the design of a high frequency ultrasonic transducer [2]. This is a complex and expensive process. Ultrasound can be emitted to and detected from the target located in solid, liquid or a gaseous coupling medium depending on the application. This coupling medium presents an impedance mismatch to the transducer. Especially, when used in fluids, this mismatch is quite large that impacts the performance of the transducer greatly. For example, when these piezoelectric based transducers are used in air, the mismatch in impedance is of the order of 10<sup>5</sup> which results in a large attenuation of ultrasound signals in air i.e. poor efficiency and also leads to narrow bandwidth operation of the transducers. The impedance of piezoelectric layer is  $35 \times 10^6$  kg s/m<sup>2</sup> and that of air is 400 kg s/m<sup>2</sup>. Due to the large mismatch between the acoustic impedance of the piezoelectric layer and the medium (air, water etc), a matching layer is provided between piezoelectric layer and the medium. Placing such a layer lowers the acoustic energy transmitted to the medium and also reduces the bandwidth. Also, depositing a matching layer with precise thickness for high frequency operation is a very challenging process step in the manufacturing of high frequency tranducers [3]. Some other drawbacks of the piezoelectric transducers are manifested by the fact that their operating frequency span is directly related to the size. For high frequency operation, this leads to impractical design requirements. Also, piezoelectric transducers are limited in the operating temperature as they depole at relatively low temperatures [4].

#### 1.1 Motivation and research objective

Micromachined Ultrasound Transducers (MUTs) have emerged as an alternative to the conventional ultrasonic transducer over the past decades. Capacitive Micromachined Ultrasonic

Transducer (CMUT) was invented in 1990s as an electrostatic based transducer for airborne applications with operating frequencies in the MHz range [5]. These transducers overcome most of the drawbacks of the conventional piezoelectric transducers in terms of bandwidth, sensitivity and transduction efficiency. Airborne ultrasound has wide variety of applications like high resolution short distance sensing in robotics, range finding, non-destructive evaluation (NDE) and flow measurement. As the frequency of these transducers increases, the resolution increases. The limitation of conventional transducers for airborne applications due to impedance mismatch issues was described in the previous section. The CMUTs also exhibit a wide bandwidth operation in immersion applications as well. Advancements in micromachining techniques enabled the design and manufacture of miniaturized CMUTs with precisely controlled performance parameters. One of the biggest advantages of the CMUTs is its CMOS compatibility. This enables very close integration possibilities with the interface electronics. CMOS compatibility opens up the doors for a monolithic integration of CMUT and CMOS on the same wafer. Thanks to the manufacturing techniques, CMUTs inherit the advantages like batch fabrication and scalability.

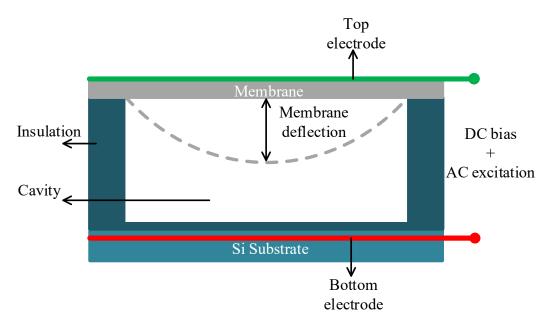

A basic cross section view of the CMUT is shown in Fig. 1.2. CMUT consist of a flexible membrane suspended over a thin gap. Insulation posts are provided to support the membrane over the silicon substrate at the bottom. The thin gap can be air filled or can be vacuum sealed. Metal electrodes are provided at the membrane on the top and the substrate at the bottom. This makes the CMUT essentially a miniaturized parallel plate capacitor with a top plate (membrane) and bottom plate (substrate). This constitutes one CMUT cell. Generally, multiple such structures are connected in parallel to form a CMUT element. CMUTs are used as both ultrasonic transmitters and receivers. To use them as transmitters, electrostatic force is applied on the membrane to cause it to vibrate with an alternating voltage. The vibration of the membrane generates ultrasound waves in the medium in which it is being used. In the receive mode, acoustic signals impinge on the CMUT membrane causing it to vibrate. These vibrations modulate the capacitance of the element which is then detected using a read-out circuit. In order to have an electro-mechanical coupling coefficient comparable to that of piezo based transducer, it is required to have a very high electric field in the cavity. This should be in the order of  $1 \times 10^8 \,\mathrm{V}\,\mathrm{m}^{-1}$  or higher [6]. The advancements in MEMS technology have enabled manufacturing of such narrow vacuum gaps with high precision. This is crucial to generate sufficient ultrasonic power in the medium. The height of the gap in-fact determines the ability of a particular CMUT to function as a transmitter or receiver. For example, a good transmitter should be able to generate a large acoustic power into the coupling medium. In order to do this, the membrane should be able to swing very wide under the applied voltage. A large gap enables this. However, a good receiver must have a narrow

4 Introduction

Fig. 1.2 Cross section view of a Capacitive Micromachined Ultrasonic Transducer (CMUT).

gap for maximum sensitivity. When the reflected acoustic waves impinge the membrane, a small vibration should be able to generate a large capacitance change and hence a large current generation should be possible.

For operation of the CMUT, a voltage V is applied across it, resulting in the deflection of the membrane towards the silicon substrate. The mechanical restoring force of the membrane counter balances this electrostatic force [7]. The force experienced by the membrane can be written as given in [5]:

$$F = \frac{1}{2}\varepsilon A \frac{V^2}{d^2} \tag{1.1}$$

where  $\varepsilon$  is the dielectric constant of the material in between the two plates, A is the surface area of the plates, d is the gap between the plates and V is the applied voltage. As it can be seen from the equation 1.1, the force experienced by the parallel plate CMUT varies quadratically with the applied voltage causing the second harmonic to be generated [5]. To operate the CMUT with the first harmonic of the applied voltage, a dc bias voltage is first applied on the CMUT, and then an ac voltage is superimposed over it so that the total voltage applied across the CMUT is given by:

$$V(t) = V_{bias} + V_{ac}cos(\omega t + \phi)$$

(1.2)

If we make the bias voltage much larger than the ac voltage, the time varying electrostatic force varies linearly with the applied ac voltage and can be written as:

$$F(t) = \frac{\varepsilon A V_{bias} V_{ac}}{d^2} cos(\omega t + \phi)$$

(1.3)

It can be said that applying the bias voltage helps to linearize the force. Further, the receive sensitivity of the CMUTs increases due to the spring softening effect [8]. Due to the applied bias voltage, the top CMUT membrane moves closer to the substrate. This makes the device more sensitive to any membrane displacement when an external acoustic force is applied to it. This improves the CMUT performance in the receive mode. When the bias voltage is increased further, the membrane deflection also increases. At a certain voltage, the mechanical restoring force will not be able to counter balance the electrostatic force and the membrane collapses to the substrate. This voltage is called the collapse voltage or pull-in voltage [7]. It was reported in literature [4], [9] and [10] that the CMUTs should be biased close to their collapse voltage to maximize the transduction efficiency. Conventionally, an external RC bias tee circuit is implemented to apply the desired HV dc bias voltage to the CMUT. It has to be made sure that the sum of the dc and ac voltage does not go beyond the collapse voltage of the CMUT.

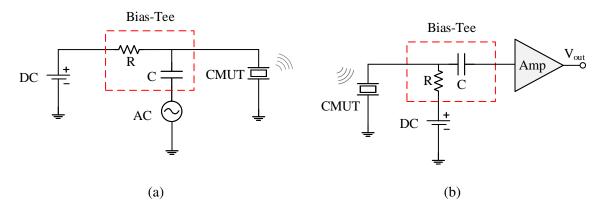

Fig. 1.3 (a) Circuit used to interface the CMUT when operated as an ultrasound transmitter; (b) Circuit interface for the CMUT when used as an ultrasound receiver.

To operate the CMUT in the transmit mode, the circuit shown in Fig. 1.3a is used conventionally. The bias tee circuit is shown in the red dotted box. As it can be seen, the ac voltage is superimposed over the dc bias to actuate the CMUT to generate the ultrasound waves. The receive mode operation of the CMUT is enabled using the electrical circuit interface shown in Fig. 1.3b. The dc bias needs to be applied for the proper operation of the CMUT as explained above. The ac drive is removed now. A pre-amplifier circuit is now connected in the receive path to which the signals generated by the CMUT are ac coupled.

6 Introduction

This thesis aims to address the following problems:

• Investigate circuit architectures to design a CMUT transceiver system which eliminates the need to use an external HV bias tee circuit to the CMUT. The R and C in the bias tee are quite large value components, hence from a cost effective point of view it is not practical to integrate it on chip.

- As explained earlier, the receive sensitivity is optimum when the CMUTs are biased close to their pull-in voltage. With the standard driving circuit as shown in Fig. 1.3, the dc and ac voltages combined should be below the maximum allowed voltage of the CMUT. This results in a dc bias voltage which is much lower than the pull-in voltage. Hence, the interface circuit should be capable of maximizing the CMUT transduction sensitivity.

- Eliminate the high voltage isolation switch in the receive path in order to improve the receiver noise performance and lower the chip area.

- Design of a low power transmit beamforming circuit which is integrated as a single chip solution with the transceiver chip.

## Chapter 2

## **Ultrasound System**

## 2.1 Conventional CMUT driving architecture

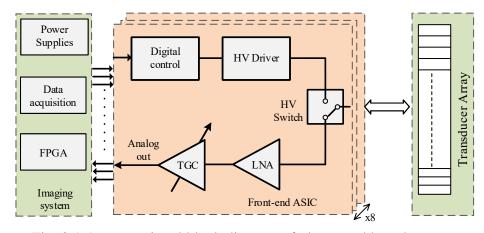

Fig. 2.1 A conventional block diagram of ultrasound based system.

A CMUT can be used as a transmitter, receiver or both depending on the desired operation. In the pitch-catch mode of ultrasound operation, one transducer is used as a transmitter of the acoustic signals and another transducer is used solely as a receiver. In the pulse-echo mode of operation, a single transducer is used as both transmitter and receiver. Most often, a pulse echo mode of operation is desired to reduce the element count. A block diagram of a conventional multi-channel ultrasonic imaging system used for pulse-echo mode of operation is shown in Fig. 2.1. Here an 8 channel front-end application specific integrated circuit (ASIC) interfaces a CMUT array. The back-end imaging system provides the required low voltage and HV power supply signals, control signals and the necessary signal processing operation of the received signals are carried out. As the ASIC contains circuit blocks for

performing both the transmit and receive operation, it can be called an ultrasound transceiver ASIC.

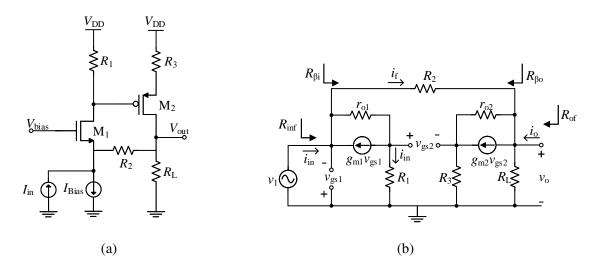

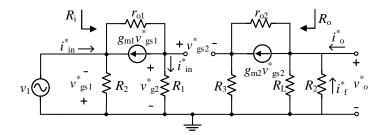

The transmit path of the ASIC consist of the HV driver/pulser circuit which generates the necessary HV ac signals at the desired frequency that are applied to the CMUT. A digital control block provides the low voltage control signals to the driver circuit. A HV switch is used to isolate the low voltage transistors in the receive signal chain from the HV signals. This switch is appropriately controlled to change from the transmit to the receive phase. In the receive path, a low noise pre-amplifier is used to amplify the signals generated by the incident ultrasonic waves. As CMUTs are high impedance sensors, a transimpedance amplifier (TIA) will be used to pre-amplify the signals. This is sometimes followed by a time gain compensation circuit (TGC) which adjusts its gain with time. In this thesis, the TGC circuit is not implemented.

Fig. 2.2 shows the interface circuit architecture for a single CMUT element to perform a pulse-echo operation in the conventional way. It is desired to keep one end of the CMUT (the one that faces the user) at ground or at low voltage for safety purpose. The HV dc bias voltage is applied through an RC bias tee circuit. This is basically a low-pass filter. The pulses from the HV pulser circuit is ac coupled through the HV capacitor during the transmit phase. The corresponding pulse waveforms can be seen in the figure. The transmit-receive (TX-RX) switch can be implemented with a HV MOS transistor. As shown in the figure the HV MOSFET will be represented with a thick drain terminal in the rest of this thesis. These devices have a higher  $V_{DSmax}$  and  $V_{BSmax}$ , however the  $V_{GSmax}$  is restricted to the standard low voltage digital levels. Appropriate control signals should be applied to the TX-RX switch. In the receive phase, the HV switch is closed to receive the current signals which are generated by the CMUT when the echos cause the membrane to vibrate thereby modulating the CMUT capacitance. The HV output of the pulser is kept at a high impedance state.

#### 2.2 Proposed CMUT driving architecture

As can be seen from the previous section, an RC bias tee is required to apply the necessary bias voltage to the CMUT. The resistor and capacitor values required are large which makes it impractical from a cost-effective point of view to integrate them on chip. It is desired to have a closely integrated sensor solution with the CMUT and electronics to make it possible to develop portable ultrasonic imaging systems. Further, improvement in signal to noise ratio also facilitates better imaging capabilities. For such closely integrated systems, eliminating the off-chip components should be a priority. Especially in applications like ICE and IVUS, in-probe ASICs are used which require reduced cable count and external

Fig. 2.2 A conventionally used driving structure for a pulse-echo operation.

components [11] [12]. Further, with the driving structure shown in Fig. 2.2, the total voltage applied to the CMUT (dc bias + ac) should be below the collapse voltage of the CMUT. It has been demonstrated that the electro-mechanical coupling efficiency is optimum when the CMUTs are biased close to their collapse voltage [10] [7]. For maximum transmit efficiency, an ac signal is superimposed over a HV bias making sure that the sum does not drive the CMUT into collapse mode. However, in the receive mode, only the dc voltage is applied to the CMUT and this is much lower than the optimum point. For the interfacing structure shown in Fig. 2.2, this results in a receive sensitivity which is reduced. In [13], an on-chip adaptive biasing scheme was implemented to boost the receive sensitivity. An adaptive dc voltage will be added to the existing dc bias to take total voltage close to the collapse voltage. This approach is however not very area efficient as additional circuit blocks like on chip DC-DC converters are needed.

In this thesis, a novel interfacing architecture is proposed that eliminates the need to have an external bias tee circuit for dc biasing as well as improve the receive sensitivity of the CMUT. The proposed structure can be seen in Fig. 2.3. A two-level pulsing scheme is used where the HV pulser switches between two high voltage levels HV1 and HV2 during the transmit phase. This is equivalent to applying a HV dc and superimposing an ac signal. In the receive phase, the pulser output is pulled to the higher of the two high voltage levels. By choosing the HV1 close to the collapse voltage of the CMUT, it is possible to operate the transducer at its optimum electro-mechanical coupling efficiency in the receive mode.

10 Ultrasound System

Fig. 2.3 The proposed transmit-receive structure for the pulse-echo operation.

Two switches S1 and S2 are provided in the receive path which can be implemented using low voltage MOSFETs. The CMUT acts like an isolator for the receive path from the HV transmit path in this case. The switches are controlled in such a way that during the transmit mode, the switch S2 closes and connects the CMUT electrode 2 to the ground. S1 is kept open during this phase. When the operation is switched to the receive mode, S2 is opened and S1 connects the CMUT terminal to the input of the TIA. The current generated by the CMUT while receiving an echo is then input to the TIA. The CMUT electrode 2 will have a low dc voltage which is set by the bias voltage of the TIA. This ensures that this CMUT terminal will always be at a low voltage or ground and can be safely exposed to the user in a product. This approach helps us to eliminate the use of HV MOSFETs from the receive path. This is beneficial in lowering the silicon area and also lowers the parasitic capacitance at the TIA input which improves the noise performance of the TIA. The phases controlling the switching operation and a representative pulse waveform applied to the CMUT can also be seen from Fig. 2.3.

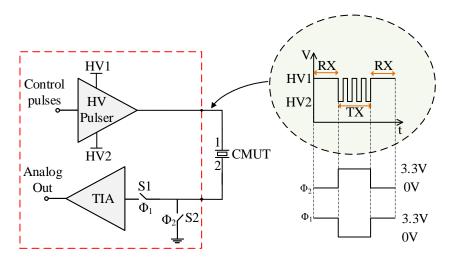

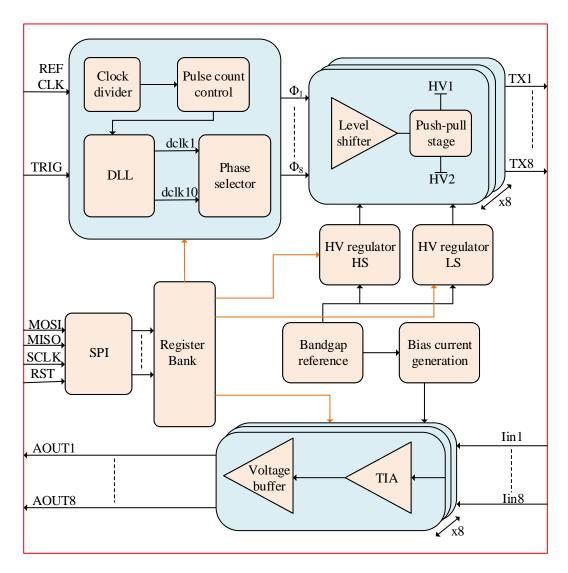

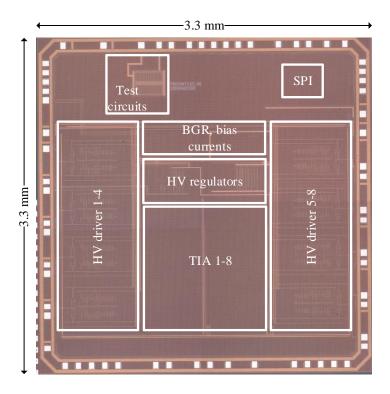

## 2.3 Ultrasonic Transceiver Chip Architecture

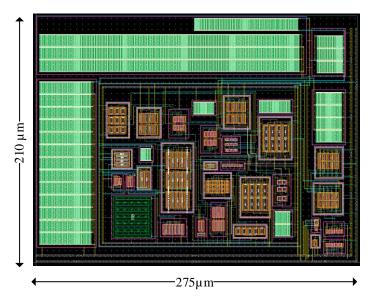

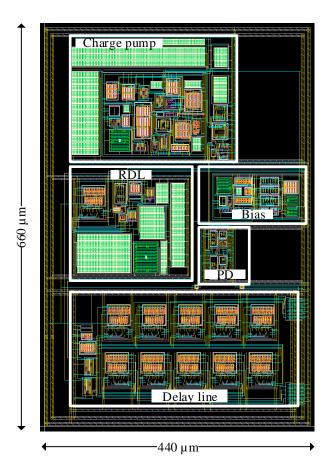

An ultrasonic transceiver chip with transmit beamforming capability has been designed during the framework of this doctoral work. The new driving architecture explained in the previous section enables the integration of the dc biasing on chip. Three versions of the transceiver chip have been designed using a 0.18 µm HV SOI process XT018 from XFAB during the project time frame, each with incremental performance additions. The first two versions of the chip named ProTaktilUS\_A0 and ProTaktilUS\_B0 are fully characterized.

A block diagram representation of the final ASIC version is shown in Fig. 2.4. The chip is named ProTaktilUS\_C0 and is submitted for fabrication.

Fig. 2.4 Block diagram representation of the designed CMUT transceiver ASIC.

12 Ultrasound System

Fig. 2.5 Microphotograph of the ProTaktilUS\_A0 chip.

Fig. 2.6 Microphotograph of the ProTaktilUS\_B0 chip.

Fig. 2.7 Chip layout of the ProTaktilUS\_C0 chip which is under fabrication.

#### 2.4 High Voltage Process Technology

Several foundries offer different processes for chip manufacturing. Depending on the project requirements, an appropriate process selection is a key step in the execution of any ASIC design project. In this section, the process used for this work is briefly introduced.

A high voltage CMOS manufacturing process is required for the design of the CMUT transceiver chip. The pulser circuit in the transmit path demands the use of high voltage transistors. As the target voltage requirement for this project is  $60\,\mathrm{V}$  for the pulser, a technology that supports this voltage level is needed. There are few fabs that offer such high voltage processes. The  $0.18\,\mu\mathrm{m}$  high voltage process from XFAB is used for this work. Some of the key desired features for an integrated HV processes are low  $R_{on}$ , low self heating and faster switching.

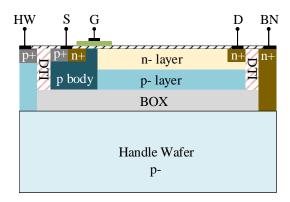

Fig. 2.8 Cross section view of a super junction high voltage NMOS (LNDMOS) transistor [14], [15].

A HV MOS transistors based on partial SOI technology is shown in the Fig. 2.8. Deep Trench Isolation (DTI) is used for lateral isolation of the devices. The lateral super junction formed by horizontal n and p layers in the top silicon which sets the voltage rating of the device. The device consist of a top silicon layer on top of a Buried Oxide (BOX) layer. The SOI diode is reverse biased by connecting the terminals BN (diode cathode) and the HW (anode) to the appropriate high voltage levels. This structure allows for small isolation distance between the devices on the chip. This is very critical for this work where multiple HV and LV ultrasonic channels need to be integrated on the same die. The technology also provides up to 6 metal layers including a thick metal option [16].

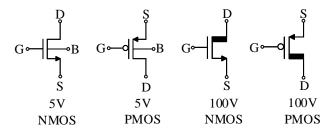

For the design of the low voltage circuits, 5 V MOSFETs are used from the process. The transistor symbols used for designs are shown in Fig. 2.9. As it can be seen, the HV MOSFETs are drawn with a thicker drain terminal. This shows the high voltage tolerance of the drain-source terminals. The 100 V devices are used for the design of the HV circuits

in this work. This means that the maximum  $|V_{\rm DS}|$  and  $|V_{\rm DB}|$  that can be applied across the MOSFETs are 100 V. These transistors have a thin gate oxide like the standard low voltage MOSFETs, hence the maximum  $|V_{\rm GS}|$  is 5 V. This helps to achieve better control over the threshold voltage and also they are in the standard  $V_{\rm th}$  value. For high gate to source voltages, the transistors must have a thicker gate-oxide. This leads to reduced transconductance and poor threshold voltage control [17]. The bulk terminals are not shown for the HV MOSFETs as they are connected to the source. For the designs used in this thesis, the 5 V MOSFET's bulk is connected to ground and VDD for NMOS and PMOS respectively. Hence, they will not be shown in the schematic explicitly unless they are connected differently.

Fig. 2.9 Symbols used for the different MOSFETs used in designs.

### **Chapter 3**

# Integrated Circuits for CMUT Transceiver Interface

#### 3.1 Background

The interface electronics design plays a crucial role in an ultrasound system as much as the transducer design. Conventionally, these electronic circuits are placed in the back-end imaging system which connects to the probe with long coaxial cables. So, each transducer element needs one cable connecting it to the circuits. As explained in the previous chapter, the advancement of CMUTs have enabled the development of large 1D and 2D arrays of CMUTs. In such cases, it is not practical to run long cables from the transducer probe to the imaging system. Also, since the aim is to develop a portable, hand-held ultrasound imaging system, it is imperative that we build a system where the sensor solution consisting of the transducers and interfacing electronics are closely integrated. A hybrid multi-chip solution or a monolithic solution is desired for this. This drives the design of application specific integrated circuits, which has both the high voltage transmitter circuitry and the low voltage receive and other control circuits on the same chip. A low-power, area efficient HV transceiver ASIC with 8 channels is designed in this work with the aim of interfacing an 8 channel CMUT array.

This chapter presents the design of the key circuit blocks of the CMUT interface ASIC. The circuit topology selection and circuit analysis are presented first, then a systematic approach to the design is presented. This is followed with relevant simulation results and finally, the measurement results from the tape-outs are also presented.

#### 3.2 High Voltage Transmit Pulser Circuit

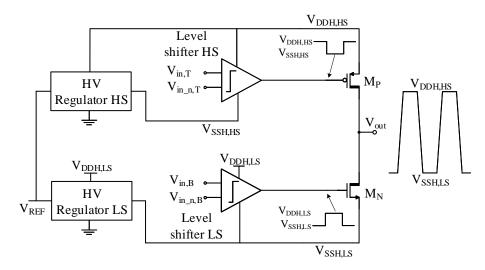

As explained in Chapter 2, a two-level HV pulser is one of the most critical block in the transmit path of the CMUT transceiver chip of this thesis. A block diagram representation of the pulser circuit is shown in the Fig. 3.1. The pulser circuit at the core has two high voltage transistors  $M_P$  and  $M_N$  at the output forming a push-pull stage. The circuit switches between the two high voltage levels  $V_{DDH,HS}$  and  $V_{SSH,LS}$ . These output stage transistors are driven by two level shifters. The level shifter on the high side drives the  $M_P$  and the level shifter on the low side drives the  $M_N$ . The level shifters convert the low voltage control signals ( $V_{in,T}$ ,  $V_{in,n,T}$ ,  $V_{in,B}$  and  $V_{in,n,B}$ ) in the 0 V - 3.3 V domain to the HV levels. The low voltage control signals are generated using a 4 phase non-overlapping clock generator circuit.

Two HV linear regulators form critical circuit blocks in the pulser circuit. The linear regulator on the high side (HV Regulator HS) is basically used to bias the protection transistors in the high side level shifter. The regulator on the low side has a more demanding design requirement. As can be seen from the Fig. 3.1, the low side regulator also serves as the bottom side rail of the transistor  $M_N$ . During the discharge phase of the CMUT, a large amount of current is discharged through  $M_N$ . When used for a CMUT array, this rail should be able to sink a large amount of current ( $\sim$  few tens of milli-amperes). Hence, a HV linear regulator with high current sink capability is designed for this purpose.

Fig. 3.1 The top-level block diagram of the high voltage pulser circuit.

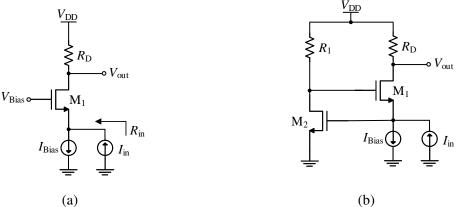

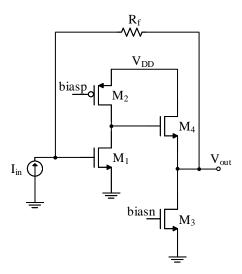

#### 3.2.1 Static level shifter based pulser design

For the design of the HV pulser circuit, different architectures from the literature have been studied. The most common type of the level shifter is based on limiting the  $V_{GS}$  by using a diode or a diode connected transistor. In Fig. 3.2, a HV pulser circuit based on a static level shifter can be seen [17] [18]. This is a cross coupled voltage mirror based level shifter from [19]. The voltage mirror structure consist of a HVNMOS M1 with a load formed by a low voltage PMOS M3. M3 is a diode-connected MOSFET whose  $V_{GS}$  sets the voltage at node  $V_a$ . The transistor M<sub>4</sub> is a pull-up transistor which makes sure that the node  $V_a$  is pulled up to  $V_{DDH}$  in the off-state.

Fig. 3.2 Static level shifter based pulser circuit

The low voltage control signal  $V_{\rm in}$  is applied to M1 and M2 is driven by its inverted signal. When  $V_{\rm in}$  is high, M1 is turned on and a current is drawn from the HV supply  $V_{\rm DDH}$ . Depending on the device dimensions, the node  $V_{\rm a}$  will have a voltage given by  $V_{\rm DDH} - V_{\rm SG3}$ . This level shifted signal is then used to drive the gate of  $M_7$  which forms the high-side transistor of the push-pull output stage. The design equations can be derived by equating the current through the transistors. When  $M_1$  is turned on by applying a  $V_{\rm DD}$ , it turns on in saturation (assuming that  $V_{\rm DDH} \gg V_{\rm DD}$ ). By equating the currents through  $M_1$  and  $M_3$ , we can write:

$$\frac{\beta_1}{2} (V_{\text{in}} - V_{\text{th}1})^2 = \frac{\beta_3}{2} [(V_{\text{DDH}} - V_{\text{a}}) - V_{\text{th}3}]^2$$

(3.1)

By re-arranging, we get:

$$V_{\rm a} = V_{\rm DDH} - \left[ \sqrt{\frac{\beta_1}{\beta_3}} \left( V_{\rm in} - V_{\rm th1} \right) + |V_{\rm th3}| \right]$$

(3.2)

where,  $\beta 1 = \mu_n.C_{ox}^{\prime}.\frac{W_1}{L_1}$  and  $\beta 3 = \mu_p.C_{ox}^{\prime}.\frac{W_3}{L_3}$

$\mu_n$ : mobility of electrons

$\mu_p$ : mobility of holes

$C'_{ox}$ :gate oxide capacitance

By properly choosing the aspect ratio of the transistors, the node voltage  $V_a$  can be set. It can be made sure that this voltage is within the limits of the gate-oxide breakdown of the technology.

Fig. 3.3 Current limited static level shifter based pulser circuit.

This basic static level shifter based design is one of the most robust and area efficient pulser design, however these have some drawbacks as well. One of the main drawbacks of this circuit is the continuous power dissipation through either side of the level shifter stage. The current drawn is limited by the device dimensions which is in turn set by the node voltage  $V_a$ . A few milli-amperes of current drawn from the high voltage supply  $V_{\rm DDH}$  can lead to a large power dissipation. This is not acceptable for a portable system where

power consumption is a very crucial parameter. An improved current-limited static level shifter based pulser circuit is shown in Fig. 3.3. Here a current limit is introduced by using the transistors  $M_9$ ,  $M_1$  and  $M_2$ . The diode connected load  $M_{10}$  sets the current through the current mirrors. The bottom side transistor  $M_{12}$  is driven by an identical level shifter. For clarity and ease of explanation, only the high side level shifter is shown here.

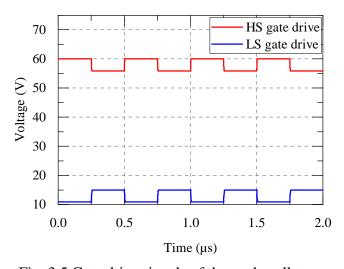

The two-level pulser circuit based on the static level shifter is designed for the HV levels of 60 V to 10 V switching. The simulation results are shown in Fig. 3.4, 3.5 and 3.6.

Fig. 3.4 High voltage output of the pulser circuit.

Fig. 3.5 Gate drive signals of the push-pull stage.

The high voltage output of the pulser circuit is shown in Fig. 3.4. As it can be seen, the pulser output switches between the voltage levels 60 V and 10 V. The low voltage control signal is applied at a frequency of 2 MHz. From Fig. 3.5, the gate drive signals of the output push-pull stage can be seen. This is in fact the output of the two level shifters. The high-side

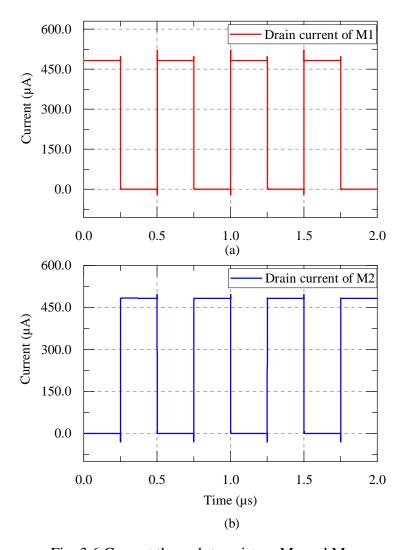

(HS) gate drive signal switches between 60 V and  $\backsim$  55 V. This ensures that the  $V_{SG}$  of  $M_{11}$  is below its  $V_{SGmax}$  (which is 5.5 V in this technology). For the low-side (LS), another level shifter up-shifts the low voltage control signal to 15 V to  $\backsim$  10 V range. Fig. 3.6 shows the current pulses through the transistors  $M_1$  and  $M_2$ . It can be seen that there is a continuous current consumption of around 480  $\mu$ A during each half cycle through either branch from the 60 V supply. This amounts to an average power consumption of 36 mW of power per pulser. For a large CMUT array, this leads to a large power budget and heating problems. The power consumption is reduced significantly with this architecture as compared to the basic static level shifter. However, the input to output delay increases with this. Hence, it is not possible to lower the currents to very low values as it affects the switching speed considerably. So, a low power architecture is desired.

Fig. 3.6 Current through transistors  $M_1$  and  $M_2$ .

#### 3.2.2 Gate charge recycled level shifter based pulser

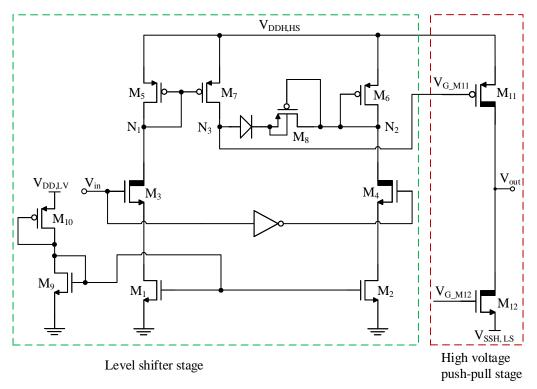

A low power level shifter architecture for driving the high side switch in a DC-DC converter of an implantable device was presented in [20]. The similar approach was previously presented for HV display driver design in [21] [22]. Power consumption from the HV rail is minimized using a gate charge recycling technique. The schematic of the gate charge recycled level shifter based pulser circuit is shown in Fig. 3.7. This is a slight modification from what is presented in [21]. Low voltage current limiting transistors  $M_1$ ,  $M_2$  and  $M_9$  limit the current consumed during each cycle.

Fig. 3.7 Gate charge recycled level shifter based pulser circuit.

An edge detector circuit (not shown in the schematic) is used to generate short duration pulses that are applied at the input HV MOSFETs  $M_3$  and  $M_4$ . When  $V_{in}$  is HIGH (3.3 V),  $M_5$  is turned ON. This turns  $M_7$  also ON which pulls the node  $N_3$  to  $V_{DDH,HS}$ . This turns the high side push-pull MOSFET  $M_{11}$  OFF. Once  $V_{in}$  goes LOW,  $M_5$  and  $M_7$  turns OFF. Also  $M_4$  is OFF which causes the node  $N_3$  to be electrically isolated and it retains its previous charge which is stored in the parasitic gate capacitance of  $M_{11}$ .

When we have a HIGH pulse at the gate of  $M_4$  and  $M_3$  stays LOW, a current flows through the diode connected transistor  $M_6$ . The node  $N_3$  is discharged through  $M_8$  and this turns ON  $M_{11}$ . Once the control signal at the gate of  $M_4$  goes LOW,  $M_4$  and  $M_6$  turns OFF. Since  $M_7$  is also OFF the node  $N_3$  is isolated and retains the gate charge of  $M_{11}$ . This way,

we can make sure that the level shifting operation is performed and there is no continuous power drawn from the HV supply. There is a current consumtion only as long as the input pulses at the gates of  $M_3$  and  $M_4$  are HIGH. This can be controlled to make very short pulses at the input. Similar to the previous section, the low side level shifter is not shown here. An identical level shifter is used to drive the low side transistor  $M_{12}$  of the push-pull stage. The circuit has been designed and simulations are performed to verify the design.

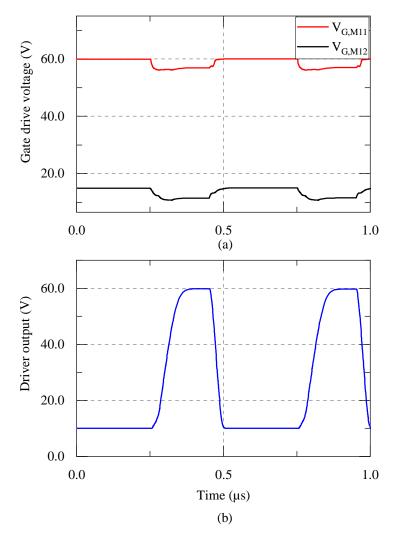

Fig. 3.8 (a) Simulation results showing gate drive signal of the low-side and high-side; (b) Output of the pulser circuit.

It can be seen from the simulation results in Fig. 3.9, that the circuit draws current from the HV supply on as long as the control input stays high. For the design used here, the pulses are 250 ns wide. A current of roughly  $50\,\mu\text{A}$  is drawn. From Fig. 3.8, the level shifted gate drive voltages can be seen. The transistor  $M_6$  can be sized appropriately to limit this voltage within the safe operating region. The charge on the gate is reset when a high pulse

Fig. 3.9 (a) Currents through the transistors M<sub>1</sub> and M<sub>2</sub>; (b) Input control signals.

appears on the other input leg. Using this architecture, it is possible to reduce the power consumption by roughly 3/4th as compared to the static current limited level shifter presented in section 3.2.1. However from simulations, it is observed that even though this topology lowers the power consumption compared to the static level shifter topology, there are certain drawbacks. It can be observed from the Fig. 3.8, the output of the pulser circuit has a large rise and fall times. The gate drive signals does not have a sharp rising and falling edge. Also, from corner simulation it is observed that it is difficult to make this circuit reliable across PVT variations. This could be due to the fact that the circuit works based on the charge storage and recycling using the parasitic capacitance at a node. Large deviation in the gate drive signals are observed across process corners. This is unacceptable for a reliable ASIC design. Also, it can be expected that with multiple such channels present on a chip, there is a possibility that during a large HV swing on another channel, a small cross coupling effect

could produce an unacceptable behavour in a neighboring channel. Hence a more reliable design is explored for the level shifter design.

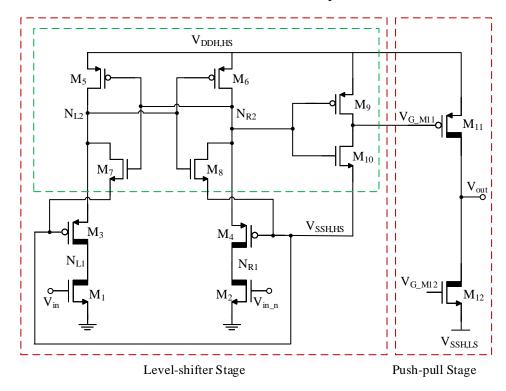

#### 3.2.3 Nanosecond delay dynamic level shifter based pulser circuit

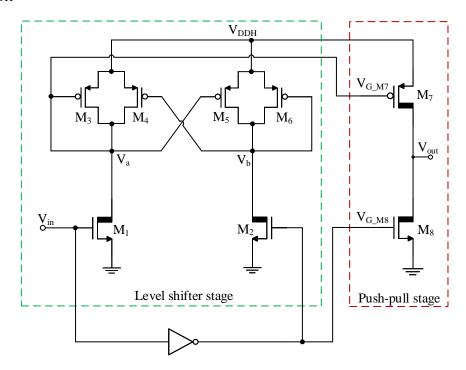

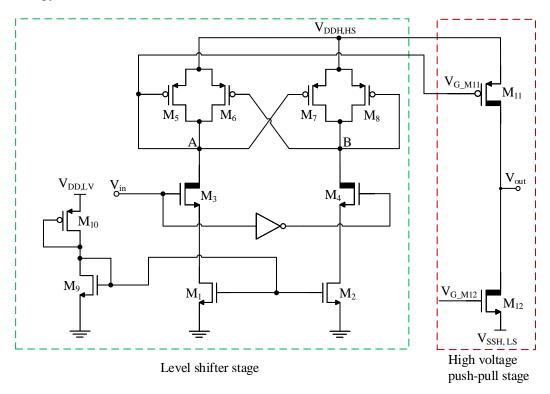

The current limited static level shifter based pulser and the gate charge recycled level shifter based pulser both have drawbacks in terms of power consumption, speed of operation and reliability. The high power consumption of static level shifter based pulser makes it unsuitable for portable or battery powered applications. Hence, a nanosecond delay dynamic level shifter based pulser circuit is designed [23] [24]. A very low power consumption design is achieved with a cross-coupled design. The circuit consumes no static power from the high voltage rails. The current is drawn from the high voltage supply only during a transition which lasts only for a few nano-seconds. The schematic of the pulser circuit is shown in Fig. 3.10. For clarity and ease of explanation only the high side level shifter is shown here. The low-side MOSFET  $M_{12}$  of the push-pull stage is driven by a similar level shifter. This is a modified version of the conventional HV level shifter reported in [25] and [26].

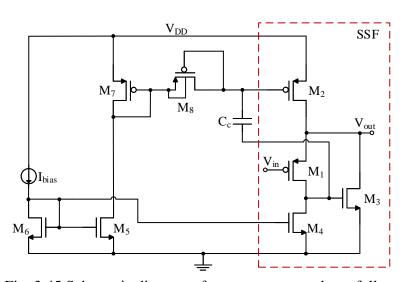

Fig. 3.10 Dynamic level shifter based pulser circuit.

The low voltage control signals drive the pull-down high voltage NMOS (HVNMOS) transistors  $M_1$  and  $M_2$ . High voltage PMOS (HVPMOS) transistors  $M_3$  and  $M_4$  protect the floating LV MOSFETs. The gates of  $M_3$  and  $M_4$  are biased to a HV level  $V_{SSH,HS}$ . The LV

MOSFETs  $M_5$  -  $M_{10}$  are floating at a HV level between  $V_{DDH,HS}$  and  $V_{SSH,HS}$ . It should be made sure that this difference is less than or equal to 5 V. Transistors  $M_7$  and  $M_8$  are used as active pull-downs which will pull the nodes  $N_{L2}$  and  $N_{R2}$  to  $V_{SSH,HS}$ . In order to ensure that the latch flips its state,  $M_7$  and  $M_8$  should be made much weaker than  $M_5$  and  $M_6$ .

The working of the circuit is explained as follows. Let us assume that initially the node  $N_{L2}$  is pulled to  $V_{DDH,HS}$  and node  $N_{R2}$  is at  $V_{SSH,HS}$ . Now, in order to flip the states, a logical high is applied to the gate of  $M_1$  (3.3 V). An inverted signal is applied to the gate of  $M_2$ .  $M_1$  pulls node  $N_{L1}$  to ground. Transistor  $M_3$  turns ON in saturation and this pulls  $N_{L1}$  down. When this node is pulled a  $V_{thp}$  below  $V_{DDH,HS}$ ,  $M_6$  turns ON and the latch flips state. The ratio of  $M_3$  to  $M_5$  decides how fast the node  $N_{L2}$  is discharged. To derive the equations for DC operation of the circuit, we can equate the current through the transistors in each branch. As the circuit is symmetrical, the equations for only one side is shown here. The other side follows the same way. At the beginning of the transition, we can take  $M_5$  to be in deep-triode region of operation. The current through this transistor can be written as:

$$I_{D5} = K_{p5} \left(\frac{W}{L}\right)_5 (V_{SG5} - V_{th5}) V_{SD5}$$

(3.3)

$$I_{D5} = K_{p5} \left(\frac{W}{L}\right)_5 (V_{DDH} - V_{SSH} - V_{th5}) V_{th6}$$

(3.4)

Since M<sub>3</sub> turns ON in saturation, the current equation can be written as:

$$I_{\rm D3} = \frac{K_{p3}}{2} \left(\frac{W}{L}\right)_3 (V_{\rm SG3} - V_{\rm th3})^2 \tag{3.5}$$

$$I_{\rm D3} = \frac{K_{p3}}{2} \left(\frac{W}{L}\right)_3 \left(V_{\rm DDH} - V_{\rm th6} - V_{\rm SSH} - V_{\rm th3}\right)^2 \tag{3.6}$$

Combining (3.6) and (3.4) to get the aspect ratio, we can write:

$$\frac{(W/L)_3}{(W/L)_5} = \frac{2 \cdot K_{p5} (V_{\text{DDH}} - V_{\text{SSH}} - V_{\text{th5}}) V_{\text{th6}}}{K_{p3} (V_{\text{DDH}} - V_{\text{th6}} - V_{\text{SSH}} - V_{\text{th3}})^2}$$

(3.7)

Similarly,  $M_1$  is sized relative to  $M_5$  to ensure sufficient current to flip the state of the latch. The current in  $M_1$  can be written as:

$$I_{\rm D1} = \frac{K_{p1}}{2} \left(\frac{W}{L}\right)_1 (V_{\rm in} - V_{\rm th1})^2$$

(3.8)

Combining (3.8) and (3.4), we can write;

$$\frac{(W/L)_1}{(W/L)_5} = \frac{2 \cdot K_{p5} (V_{\text{DDH}} - V_{\text{SSH}} - V_{th5}) V_{th6}}{K_{p1} (V_{\text{in}} - V_{\text{th1}})^2}$$

(3.9)

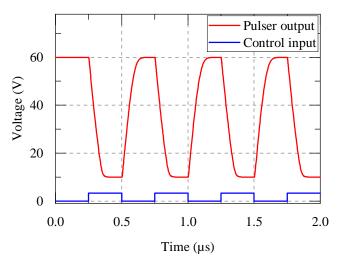

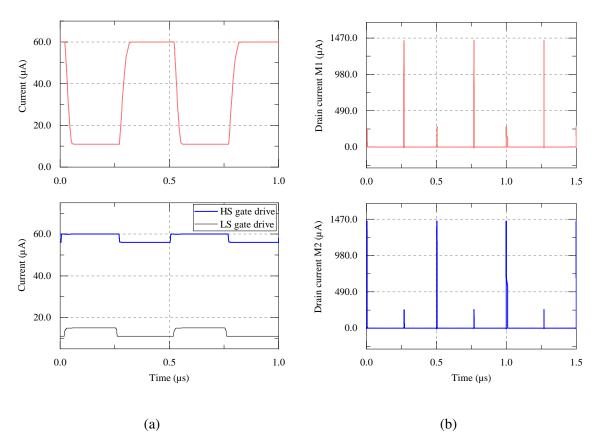

Using (3.9) and (3.7), we can size the MOSFETs in the level shifter. In the equations, only sizing information for  $M_1$ ,  $M_3$  and  $M_5$  are shown. The MOSFETs on the right branch  $M_2$ ,  $M_4$  and  $M_6$  follows the same design criteria. Post-layout simulations are performed to verify the design under various operating conditions before the tape-out. Some of the key simulations are shown here. It can seen from Fig. 3.11 (a) the gate drive control signals of the output push-pull stage. The level shifters make sure that transistors  $M_{11}$  and  $M_{12}$  have a HV level shifted control signal which is within the maximum allowed gate-source voltage limit. Fig. 3.11b shows the switching current through  $M_1$  and  $M_2$ . It can be seen that a current of around 1.4 mA is drawn from the HV supply only during a transition. During the remaining times, there is no static current drawn from the HV supply by the level shifter. This makes the designed pulser circuit very useful for low-power applications.

Fig. 3.11 (a) Post-layout simulation showing the HV pulser output and the high side and low side gate drive voltages of the push-pull stage; (b) Simulation showing the drain currents through the transistors  $M_1$  and  $M_2$ .

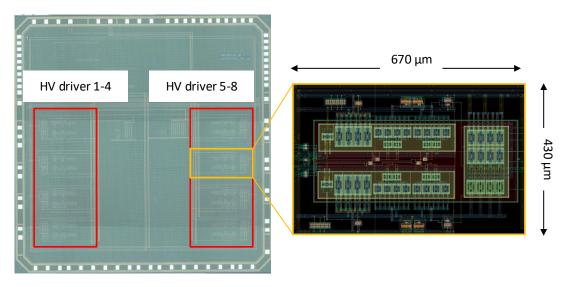

Fig. 3.12 Die photo and layout of the pulser circuit highlighted.

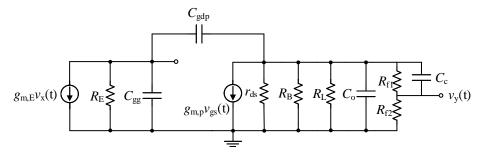

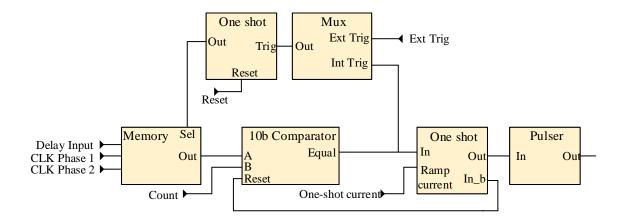

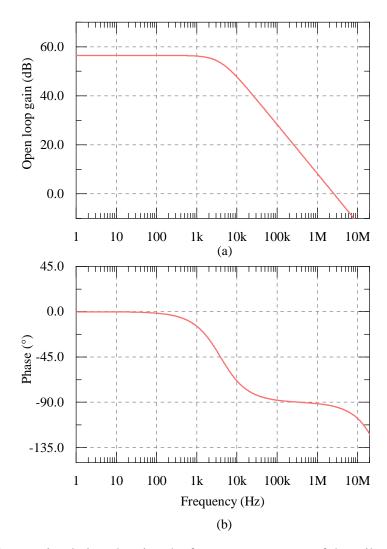

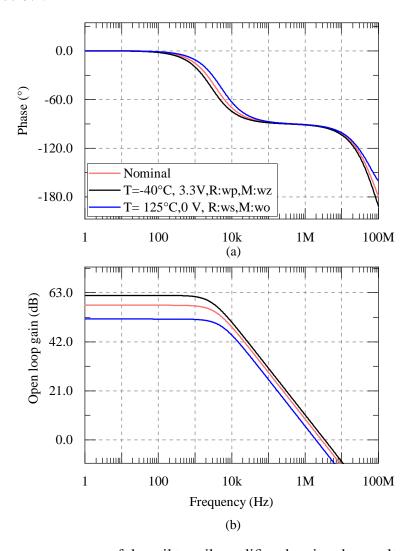

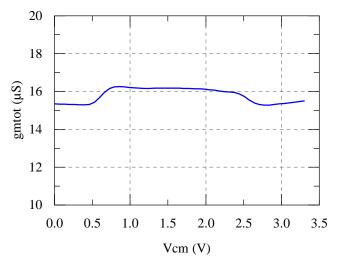

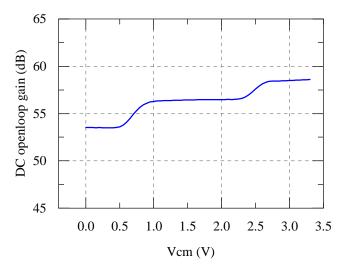

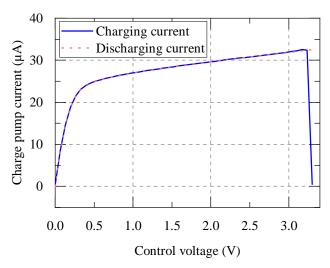

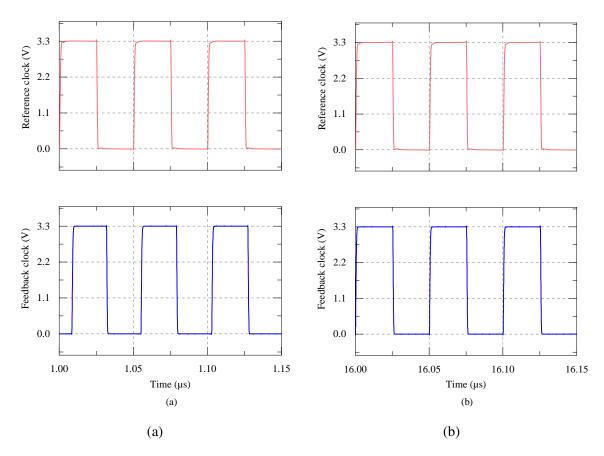

#### Frequency control and pulse counter